| IP명 | A 10 GHz Digital PLL Employing Pseudo-Differential DTC for DTC Cover Range Reduction | ||

|---|---|---|---|

| Category | Mixed | Application | Wireless and wired communication ICs |

| 실설계면적 | 3㎛ X 1㎛ | 공급 전압 | 1.0V |

| IP유형 | Hard IP | 동작속도 | 10 GHz |

| 검증단계 | Silicon | 참여공정 | HM-2501 |

| IP개요 | 본 IP는 Pseudo-Differential DTC(Digital-to-Time Converter)를 기반으로 한 저잡음 Fractional-N PLL(Phase-Locked Loop) 설계를 제안합니다. 기존의 ΔΣ Modulator 기반 PLL에서 발생하는 양자화 잡음으로 인한 지터(jitter) 및 스퍼(spur) 성능 저하 문제를 효과적으로 억제하면서, 복잡한 보정 회로 없이도 간결한 구조로 구현이 가능합니다. 특히 Pseudo-Differential 구조를 적용함으로써 DTC가 구현해야 하는 지연 범위를 절반으로 줄여, 선형성 저하와 열 잡음 증가 문제를 완화하였습니다. 이를 통해 기존 DTC 기반 Fractional-N PLL 대비 전력 소모와 칩 면적을 크게 줄이면서도, 차세대 통신 시스템이 요구하는 넓은 주파수 범위와 높은 분해능을 만족시키는 효율적이고 신뢰성 높은 주파수 합성 솔루션을 제공합니다. | ||

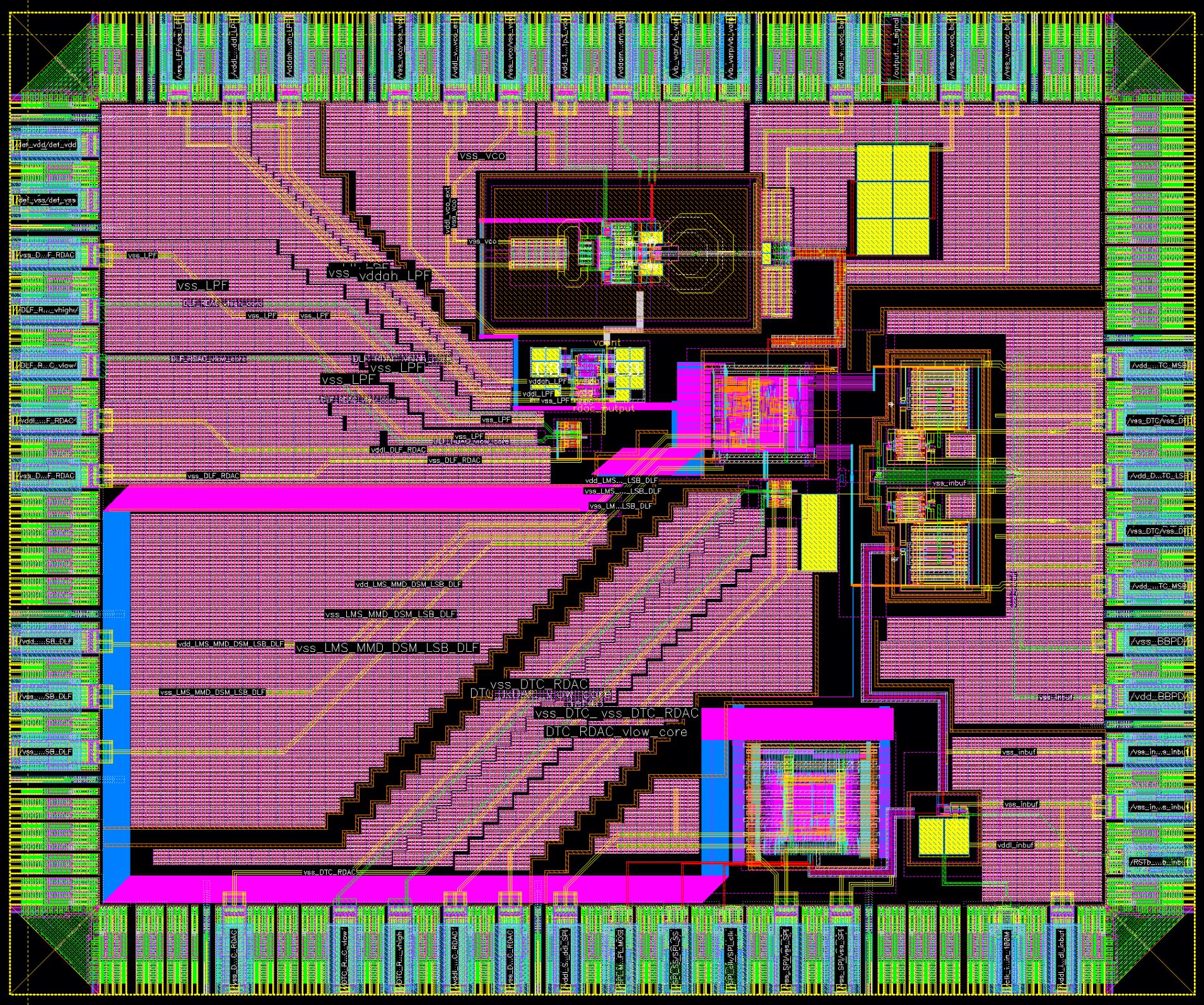

- 레이아웃 사진 -

|

|||