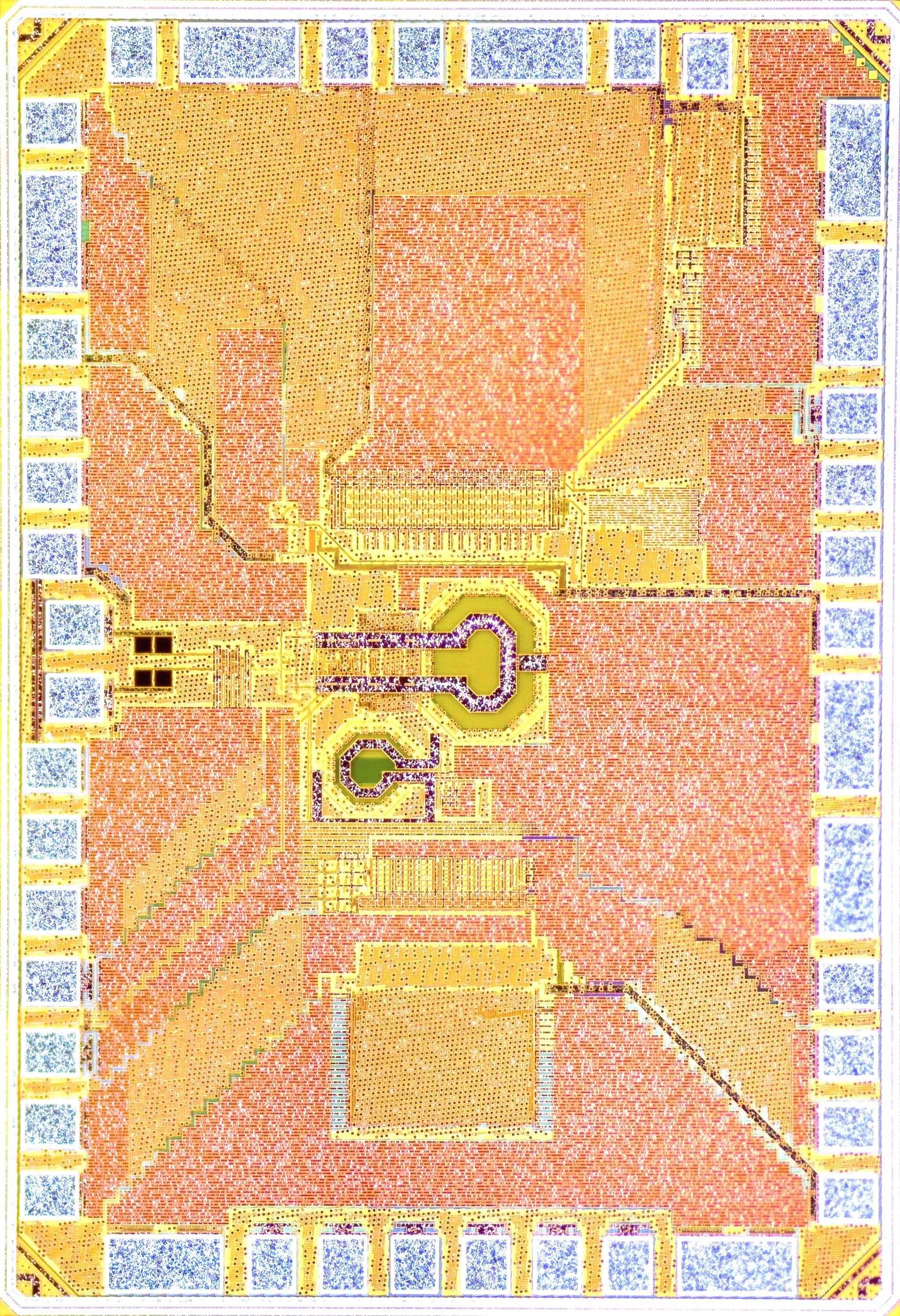

| IP개요 |

This work presents a 10.0-to-11.5GHz ultra-low-jitter fractional-N digital PLL (DPLL). The proposed quantization-errorcompensating BBPD (QEC-BBPD) minimizes both static and dynamic delays for the ΔΣM quantization error cancellation by controlling the input offset of the BBPD. It significantly reduces inband phase noise (PN) and, thus, RMS jitter of fractional-N DPLL. This work also introduces orthogonal-polynomial-based LMS multivariable calibration (OP-LMS MVC) to accelerate convergence speed with a minimal increase in the hardware complexity. This method enables more than double the convergence speed by eliminating correlations between calibration variables. The proposed DPLL is expected to achieve an excellent RMS jitter and the best FoMjitter,N among the prior-art low-jitter fractional-N PLLs. |