| IP개요 |

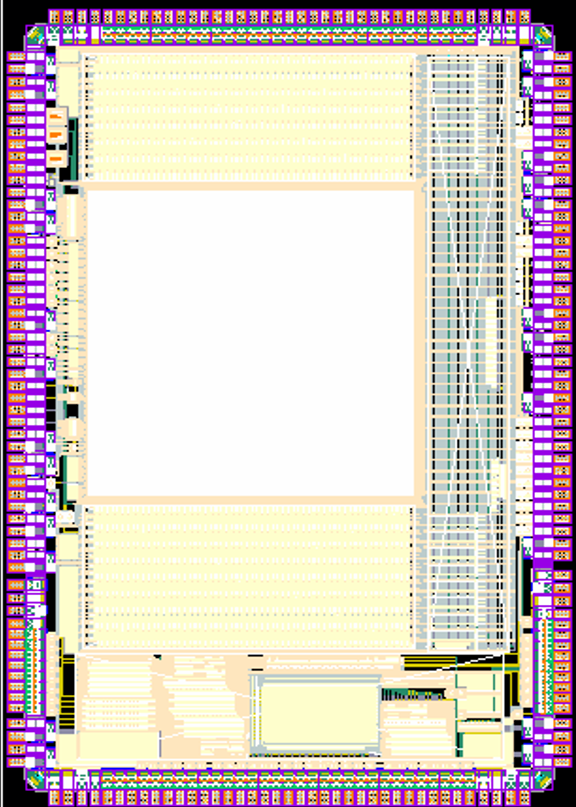

제안하는 칩은 메모리로서 단일 비트 라인 7T-SRAM 구조를 사용하여 픽셀 면적을 줄이고 작동 속도를 향상시킨 DPS 기반 CMOS 이미지 센서(CIS)에 대해 설명합니다. DPS 기반 CIS는 여러 픽셀 값이 디지털 코드로 변환되어 동시에 읽어들여지므로 높은 속도로 작동하기에 적합합니다. 이 때 픽셀 수준의 분석기-디지털 변환기(ADC)가 통합됩니다. 그러나 픽셀 크기가 크기 때문에 DPS 기반 CIS는 8개의 픽셀이 하나의 ADC를 공유하는 기술로, FPS를 증가시키지 않고 픽셀 크기를 줄이는 방식입니다. 제안된 단일 비트 라인 7T-SRAM 구조는 데이터 읽기 및 쓰기를 위해 두 개의 금속 라인, 즉 워드 라인과 비트 라인만 사용합니다. 또한 SRAM을 구성하는 트랜지스터의 크기가 기존 6T-SRAM보다 작기 때문에 면적 증가 없이 금속 라인의 수를 줄일 수 있습니다. 이를 통해 좁은 픽셀 피치에서 동시에 하나의 픽셀 데이터를 출력할 수 있는 병렬 메모리 배열을 통합할 수 있어 FPS를 증가시키고 레이아웃에서 금속 라우팅을 용이하게 합니다. 프로토타입 이미지 센서는 CMOS 180nm 표준 RF 프로세스를 사용하여 120 × 120 픽셀 배열로 제조되었습니다. 제안된 DPS 기반 CIS 픽셀은 15μm × 15μm 영역에서 25%의 필 팩터를 가지며, 이는 픽셀 공유 기술을 사용하지 않았을 때에 비해 면적이 75% 감소하고 필 팩터가 9배 증가한 것입니다. 또한 시스템 클럭 100MHz에서 6,172 FPS의 높은 프레임 속도로 작동합니다. |