| IP개요 |

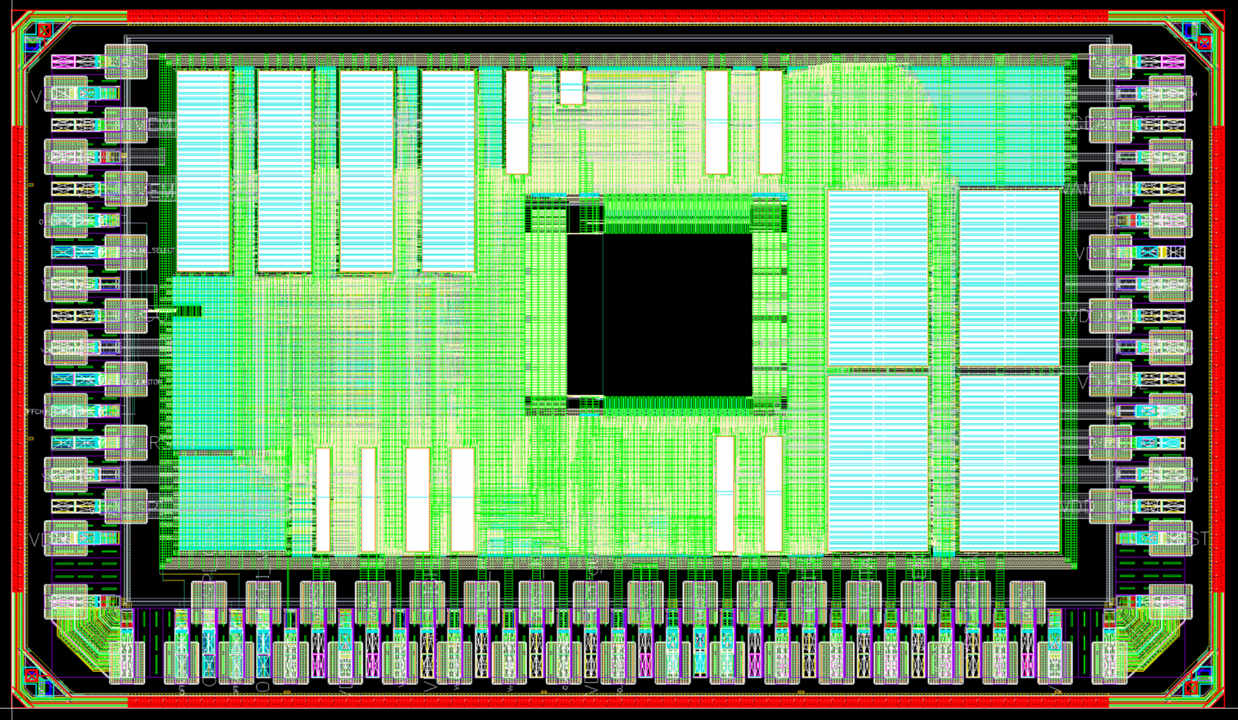

본 MPW에서는 60fps 이상의 이미지 처리 속도를 저전력으로 달성해야 하는 비전 에지 컴퓨팅을 대상으로 하는 1T1C DRAM 기반 analog Compute-in-Memory (CIM)을 활용한 가속기를 제작한다. 제시하는 CIM은 charge-steering amplifier에서 착안한 것으로, DRAM 내 모든 1T1C 셀이 연산에 참여해 높은 연산 효율을 갖는다. 이를 기반으로 실제 구동 환경에서 PVT variation에 의한 연산 오류를 모두 해결하는 analog on-chip gain calibration 회로를 구현하여 MAC macro로서 활용한다. 또한, 이 CIM macro의 charge capacity에 의해 발생하는 부분합 readout 과정과 output stationary에 특화된 dataflow를 가진 디지털 아키텍처를 설계한다. 이를 통해 행렬 또는 벡터 곱 외의 비선형 레이어를 다룬다. 해당 구조는 자율주행에서 요구하는 60fps 처리 속도를 충족시키면서도 저전력으로 동작할 수 있을 것으로 기대된다. 설계하는 회로는 TSMC 28nm CMOS 공정을 이용하며, 코어 동작 전압은 0.9V, 최대 동작 주파수는 200 MHz 이다. |