| IP명 | A Second-order Noise-shaping SAR ADC with 3-Level-Switching CDACs employing a Novel DWA | ||

|---|---|---|---|

| Category | Mixed | Application | ADC |

| 실설계면적 | 3.8㎛ X 3.8㎛ | 공급 전압 | 1V |

| IP유형 | Hard IP | 동작속도 | 80MHz |

| 검증단계 | Silicon | 참여공정 | SS28-2402 |

| IP개요 | Floating inverter based amplifier (FIA)를 사용하여 2차 노이즈 쉐이핑을 구현한 NS-SAR ADC를 제안한다. 저전압/저전력 소모의 특성을 갖춘 다이내믹 FIA를 통해 SAR ADC는 2차 노이즈 쉐이핑을 채용하면서도 전력 소모를 최소화 한다. 제안된 ADC는 split-array 타입의 capacitive DAC (CDAC)을 사용하는데 , CDAC을 구성하는 단위 커패시터 사이의 미스매치가 시스템의 성능을 저하시키는 것을 최소화하기 위하여 해당 구조에 최적화된 data weighted averaging (DWA)을 적용 하였다 제안하는 ADC 회로 는 28-nm CMOS공정을 사용하고 80MS/s의 Sampling rate으로 동작한다 . 성능은 약 88dB의 SNDR을 가지며 공급전압은 1V이고 OSR은 8이다. |

||

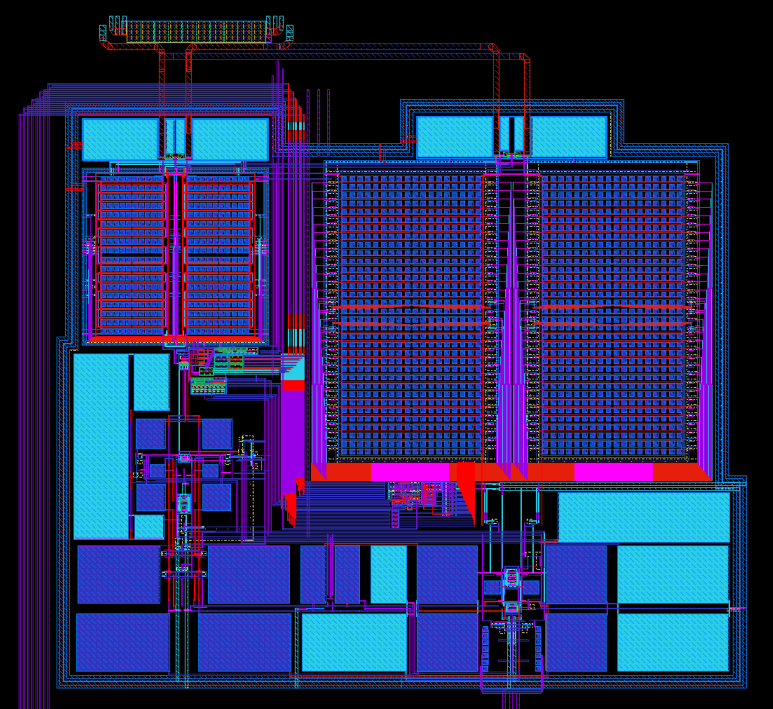

- 레이아웃 사진 -

|

|||