| IP명 | Fast Corrected Analog Duty Cycle Corrector for High-Speed Interface | ||

|---|---|---|---|

| Category | Analog | Application | High speed Interface |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1~1.2V |

| IP유형 | Hard IP | 동작속도 | 8GHz ~ 10GHzHz |

| 검증단계 | Silicon | 참여공정 | SS28-2402 |

| IP개요 | 본 설계 제안서에서 제안하는 설계 회로는 analog feedback 방식을 이용하여 8 GHz의 클록을 보정하는 DCC (Duty Cycle Corrector circuit) 이다. 연장된 잠금 시간을 보상하기 위해 이 논문은 set generator를 사용한 적분기를 도입하였다. 제안된 회로는 28nm CMOS 공정을 사용하여 설계되었다. 입력 신호의 허용 duty cycle 범위는 클럭 주파수가 4-8GHz일 때 30%에서 70%이며, 보정된 duty cycle은 50%±0.5% 범위 내에서 변동된다. 본 설계는 Samsung 28nm CMOS 공정을 이용할 예정이며 공급 전압은 1.0V이며 conventional 타입의 DCC와 성능 비교를 위해서 active area는 4m * 4m를 사용할 것이다. | ||

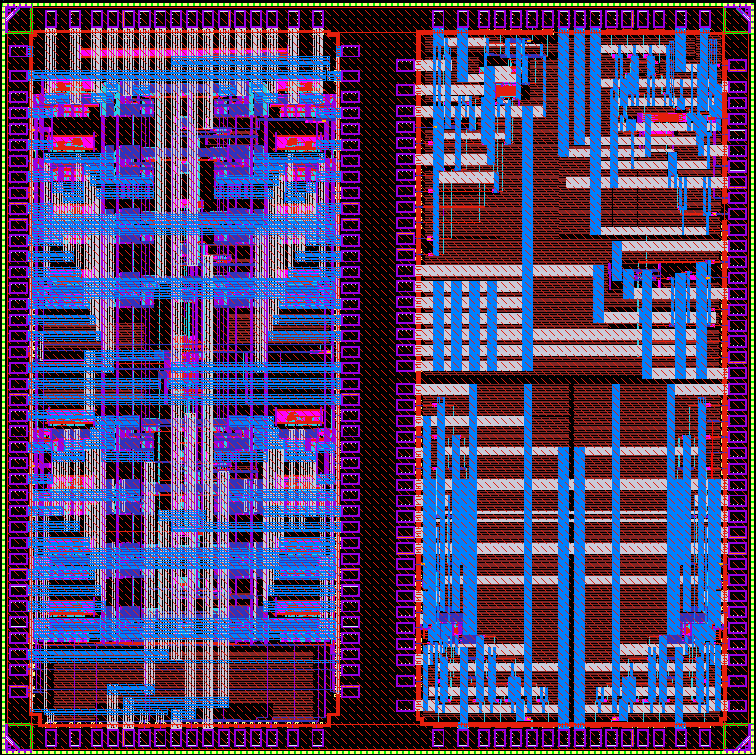

- 레이아웃 사진 -

|

|||