| IP개요 |

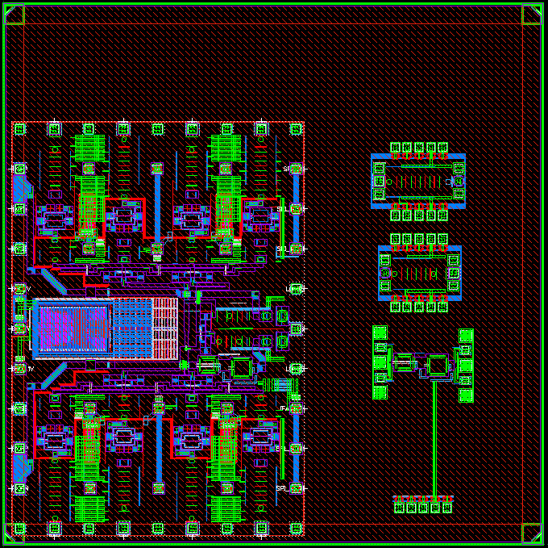

본 회로는 D-band에서 동작하는 CMOS 송수신기를 설계하고, 이를 PCB 상에서 배열하여 안테나와 결합하는 D-band 빔포밍 모듈을 제안한다. 배열된 CMOS 칩의 각 채널들의 RF I/O로부터 배열안테나의 각 요소 안테나로 연결된 채널에 존재하는 모든 채널 간 편차 및 LO, IF distribution network 등 에서 발생할 수 있는 칩 간 편차는 모듈 내 안테나 커플링을 활용한 방법을 통해 자체 테스트(Built-in Self-Test)되어 보정할 계획이다. 송수신기는 전력 증폭기, 저잡음 증폭기, 위상 천이기, Divider/Combiner, ILFM, 혼합기 및 IF증폭기의 아날로그 회로와 SPI slave와 Resistive DAC과 같은 디지털 회로로 이루어져 있다. 총 면적은 3.6 x 2.3 mm2로 구성할 예정이고 나머지 면적은 칩의 정상 동작 여부 판단을 위해 구성 블록들의 TEG로 채울 예정이다. 설계된 칩은 추후 Stud-bumping으로 각 패드에 범프를 올리고 플립칩 본딩으로 PCB와 결합해 안테나 모듈을 제작할 예정이다. 제작된 모듈의 측정은 먼저 140GHz를 포함하는 RF 통신 밴드내의 주파수에 대해 채널 간, 칩 간 편차를 자가진단방법을 통해 보정해보고 정확도를 체크해볼 예정이다. 이후 Far-field에서 주파수별 Beam-steering 특성을 확인 및 데이터 스트림을 전송하여 통신 데모를 확인해볼 예정이다. |