| IP명 | D-band Phased Array Transmitter for Next-Generation Communication Systems | ||

|---|---|---|---|

| Category | Analog | Application | Wireless communication |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1V |

| IP유형 | Hard IP | 동작속도 | 135GHz |

| 검증단계 | Silicon | 참여공정 | SS28-2402 |

| IP개요 | 설계된 가변 이득 증폭기는 2단 차동 공통소스 구조와 전류 스티어링(current-steering) 가변이득 증폭기로 구성되었다. 입력을 제외한 단간 정합은 트랜스포머를 이용하였고, 입력은 발룬을 사용하여 정합회로를 구성하였다. 130 GHz에서 최대 이득은 11.0 dB이고, 이득 조정 범위는 -9.4 dB부터 11 dB까지 20.4 dB를 가진다. 3-dB 대역폭은 118.1 GHz부터 143.5 GHz까지 25.4 GHz를 보였다. 회로는 1 V 공급 전원에서 58.22 mW의 전력을 소모한다. | ||

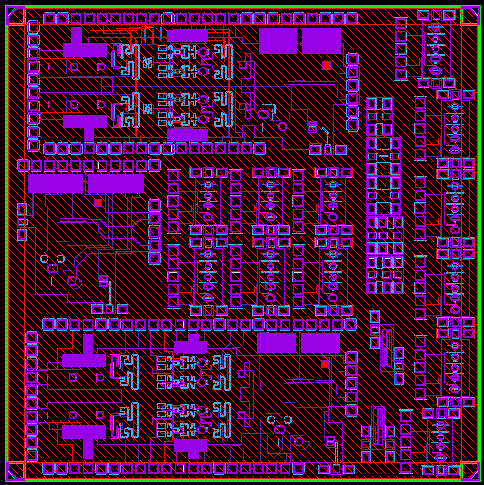

- 레이아웃 사진 -

|

|||