| IP명 | A 32-Gb/s Single-Ended PAM-4 Transmitter with Data Dependent Encoding Switching-Jitter Compensation and An Area Efficient Four-Phase Error Corrector for High Data Rate Communication | ||

|---|---|---|---|

| Category | Analog | Application | 통신 |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1V |

| IP유형 | Hard IP | 동작속도 | 10GHz |

| 검증단계 | Silicon | 참여공정 | SS28-2402 |

| IP개요 | 본 설계회로 설명서는 칩 간 고속 통신을 위한 두 가지 고속 통신 회로 IP에 대하여 설명한다. 첫 번째 IP는 PAM-4 signaling에 존재하는 switching jitter를 줄이기 위한 회로이다. 수신단에서의 valid window의 크기를 개선하는 것을 목표로 한다. 두 번째 IP는 four-phase clock 간에 존재하는 phase error corrector이다. 이는 multi-phase clock을 사용하는 고속 송수신기 회로의 안정적인 동작을 가능케하며, 송신되는 신호의 data width를 균일하게 만들 수 있다. 본 회로는 삼성 28nm RF CMOS LPP 공정을 기반으로 설계할 예정이다. 대부분의 블록에서는 28nm LPP 공정의 표준 전압인 1.0V를 공급전압으로 사용할 예정이다. | ||

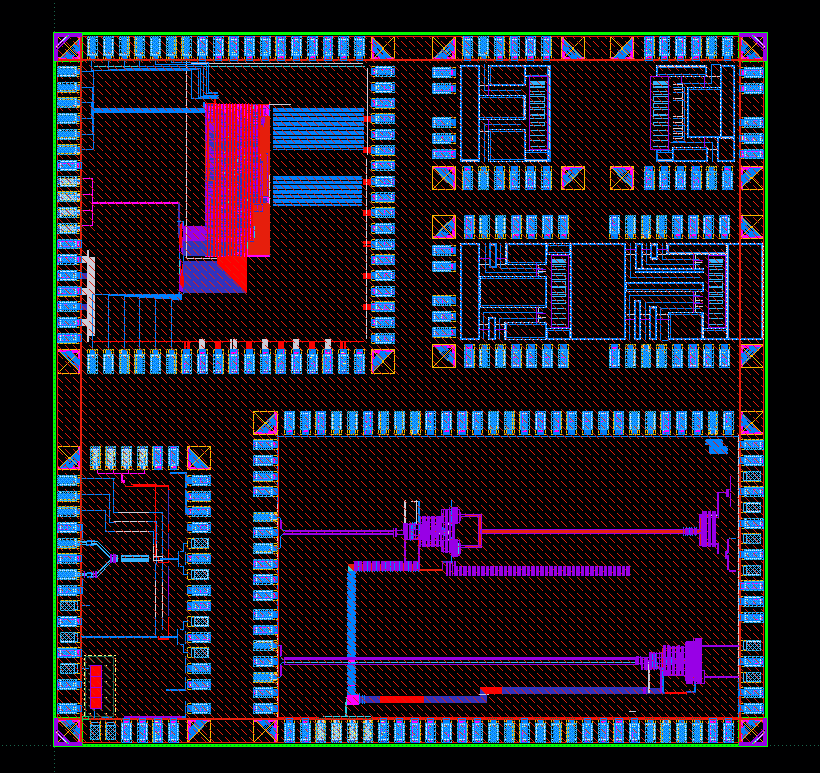

- 레이아웃 사진 -

|

|||