| IP명 | 메모리 테스트 시스템 IC 및 이를 위한 자가 테스트 구조 | ||

|---|---|---|---|

| Category | Digital | Application | 메모리 테스트 회로 |

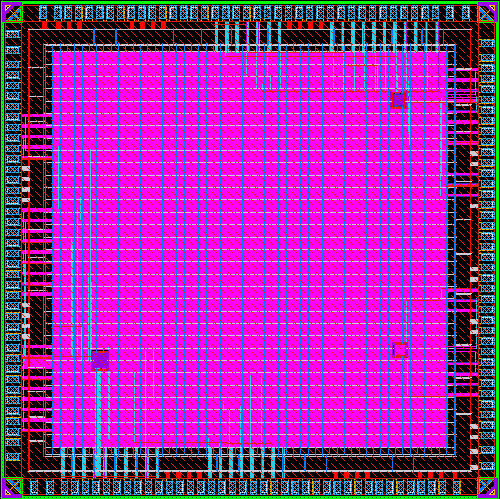

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 5V |

| IP유형 | Hard IP | 동작속도 | 50MHz |

| 검증단계 | FPGA | 참여공정 | SS28-2402 |

| IP개요 | 최근 인공지능의 발전으로 인해 초고속, 고대역폭 메모리의 수요가 증가하면서 메모리 제조업체들은 다양한 테스트 문제에 직면하고 있다. 이를 위해 메모리 테스트 시스템 IC에서 효율적인 알고리즘 패턴 생성기(ALPG)를 활용한 테스트 생성이 필수적이다. 그러나 기존 ALPG는 속도와 하드웨어 복잡도에서 한계를 드러내고 있다. 본 연구에서는 적은 하드웨어 오버헤드로 메모리 테스트 패턴 생성 속도를 높일 수 있는 새로운 ALPG 설계를 제안한다. 또한, ALPG가 포함된 메모리 테스트 시스템 IC의 신뢰성을 확보하기 위해 자가 테스트 및 수리 회로를 통합하여 메모리 테스트 시스템의 무결성을 보장한다. | ||

- 레이아웃 사진 -

|

|||