| IP명 | 2t_1c 3t_2c eDram_PIM | ||

|---|---|---|---|

| Category | Analog | Application | PIM |

| 실설계면적 | 1㎛ X 2㎛ | 공급 전압 | 1.2V |

| IP유형 | Hard IP | 동작속도 | 400MHz |

| 검증단계 | Simulation | 참여공정 | HM-2402 |

| IP개요 | 심층신경망 또는 합성곱 신경망 등의 인공지능의 급속한 발전으로 인한 매개변수 및 데이터 양의 증가는 전통적인 컴퓨팅 시스템 구조인 폰 노이만(Von-Neumann) 구조에 심각한 병목현상을 야기한다. 과도한 데이터 전달로 인한 에너지 소모 및 지연시간 증가 등의 문제점들을 해결하기 위해서, 최근 메모리 내에서 연산을 수행하는 구조인 Processing-In-Memory (PIM)에 대한 연구가 활발히 진행되고 있다. 본 MPW에서는 이진 심층 신경망을 타겟 네트워크로 하여 메모리 및 연산 효율을 높이고, 최소한의 사이즈로 학계 최고 수준의 정확도에 비견할 만한 PIM 회로를 설계하는 것을 목적으로 한다. 이를 위한 고성능 인공지능용 반도체 eDRAM을 설계했다. |

||

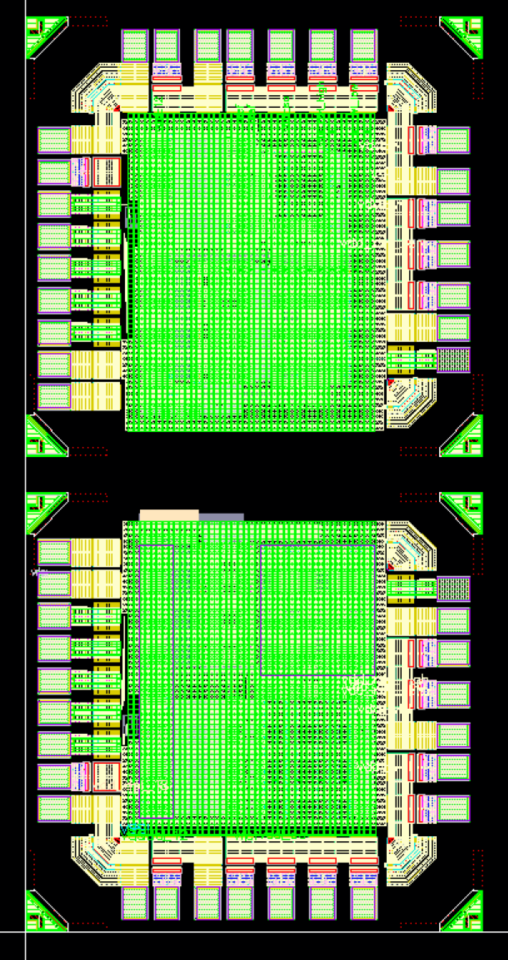

- 레이아웃 사진 -

|

|||