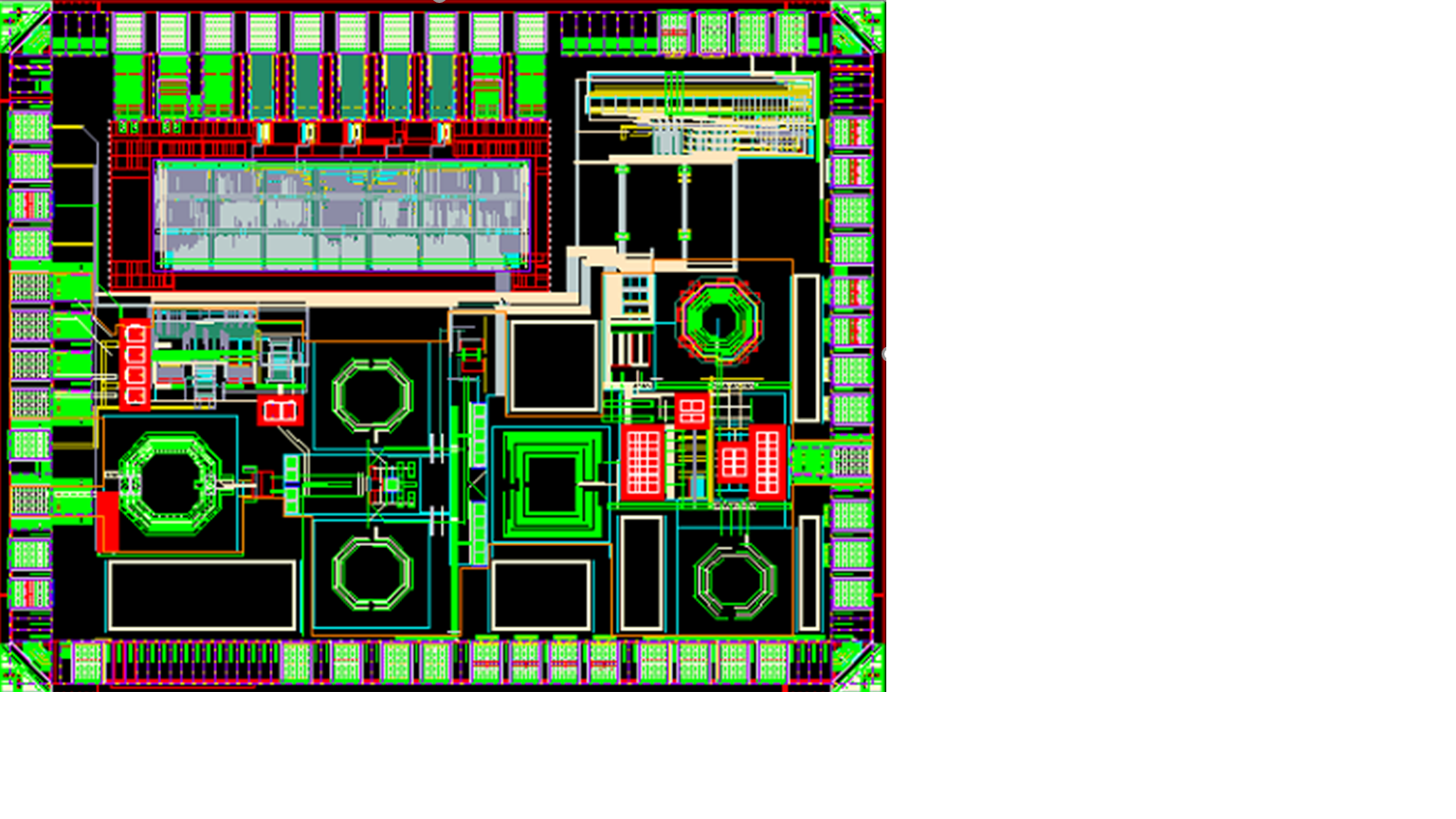

| IP개요 |

Quantum processors require qubits operating in cryogenic environments and a stable, low-jitter clock for control. Flicker noise in MOS devices worsens under these conditions. This work presents accurate, low-power frequency generation and division circuits for quantum computing. I/Q signal for qubit read-out and control is generated by a frequency synthesizer using an inverted cross-coupled and noise-circulating oscillator, which minimizes flicker noise and phase noise. The synthesizer, based on a sub-sampling phase-locked loop (SSPLL), achieves low in-band phase noise and low RMS jitter. The voltage-controlled oscillator (VCO) operates between 17 and 18.86 GHz, while an injection-locked frequency divider (ILFD) reduces the frequency to the 4-8 GHz range needed for read-out and control, minimizing power consumption. Simulations using a 100 MHz reference frequency demonstrate a robust transient response at a 4.5 GHz output frequency. The results show a low in-band phase noise of -113 dBc/Hz at a 1 MHz offset, low out-band phase noise of -130 dBc/Hz at a 10 MHz offset, and an integrated RMS jitter of 170 fs from 10 kHz to 30 MHz. Overall circuit consumes 20 mW from a 1.2V power supply. |