| IP개요 |

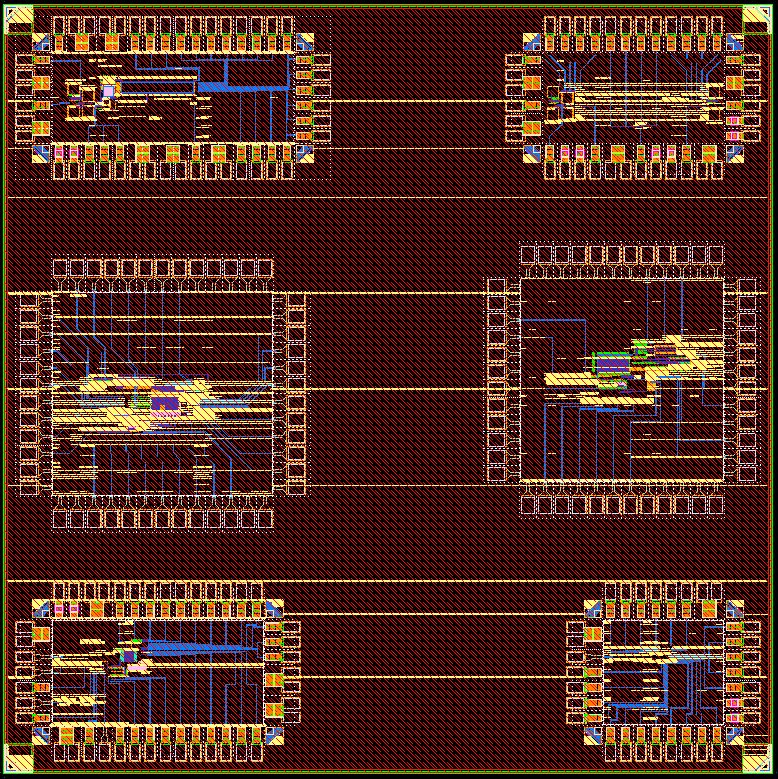

This Works introduces an innovative approach utilizing Nanoelectromechanical-Switch (NEMS) for Computing in Memory operations, addressing PVT variations. The proposed method optimizes the Mismatch detection time for the 2T1N structure by integrating with Time-to-Digital Converters (TDC), aiming for a Target Mismatch detection time within 100ns with an array size of 8X8 for Degree of Mismatch evaluation. Additionally, for the 1C1N structure, the method involves integrating with Analog-to-Digital Converters (ADC), targeting an ADC operation time within 100ns with the same array size of 8X8 for Mismatch detection voltages. The proposed system, integrating CMOS circuitry with NEM, exhibits robust performance in compensating for PVT variations in NEM Switches, enhancing the efficiency of CiM operations. |