| IP명 | 고성능 Fused Multiply-Add(FMA)를 사용한 AI 가속기 설계 | ||

|---|---|---|---|

| Category | Digital | Application | AI 가속기 |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1.8V |

| IP유형 | Hard IP | 동작속도 | 1Hz |

| 검증단계 | Silicon | 참여공정 | SF28-2401 |

| IP개요 | 본 연구는 booth radix 4와 wallace-tree를 이용하여 FP32 FMA 연산기를 구현한다. FMA로 구성된 SYSTOLIC_ARRAY는 곱셈과 덧셈을 동시에 함으로 CLOCK TIMING을 최소화 할수 있고 이외의 SPECIAL FUNCTION들도 최적화 하여 DEEP LEARNING에 필요한 행렬 연산과 SPECTIAL FUNCTION들을 가속화 한다. MNIST dataset을 이 칩을 통해 TRANSFORMER architecture 연산을 수행함으로서 추론 속도를 즉정한다. | ||

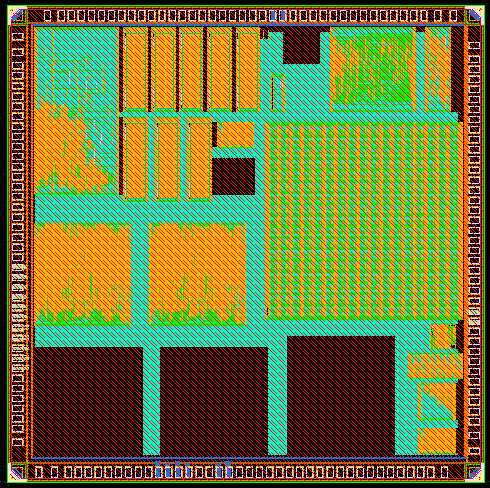

- 레이아웃 사진 -

|

|||