| IP명 | Multi-bit Computing-In-Memory MRAM Macro for Binary/Ternary Deep Neural Network and Transformer | ||

|---|---|---|---|

| Category | Mixed | Application | Process in memory |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1V |

| IP유형 | Soft IP | 동작속도 | 100MHz |

| 검증단계 | Silicon | 참여공정 | SF28-2401 |

| IP개요 | 딥 러닝 구조의 발전으로 기존 컨볼루션 신경망보다 높은 추론 정확도를 달성한 어탠션 모듈 기반의 트랜스포머가 활발히 연구되고 있다. 트랜스포머 연산에서의 메모리 병목현상을 줄이기 위해 process in memory 구조가 제안 되었다. 여러 구조 중 본 칩에서는 공간 효율도가 높은 MRAM과 높은 신뢰도의 SRAM 기반의 Process in memory을 구현 하였다. 해당 PIM 구조는는 256x64 크기의 두 SRAM 기반 macro와 기본적인 mram array로 이루어져, 각 구조의 기본적인 연산 능을 확인하기 위하여 설계되었다. | ||

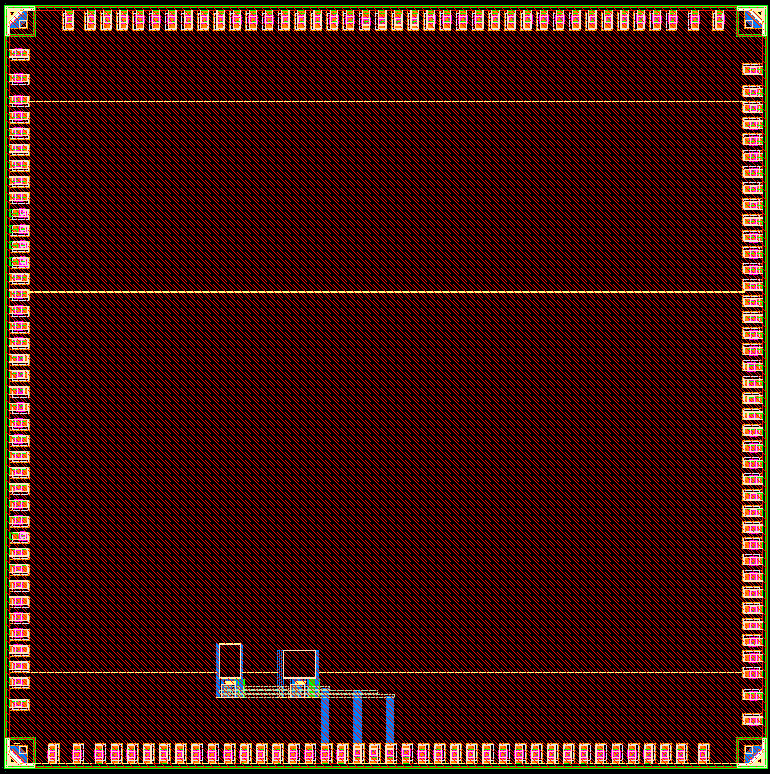

- 레이아웃 사진 -

|

|||