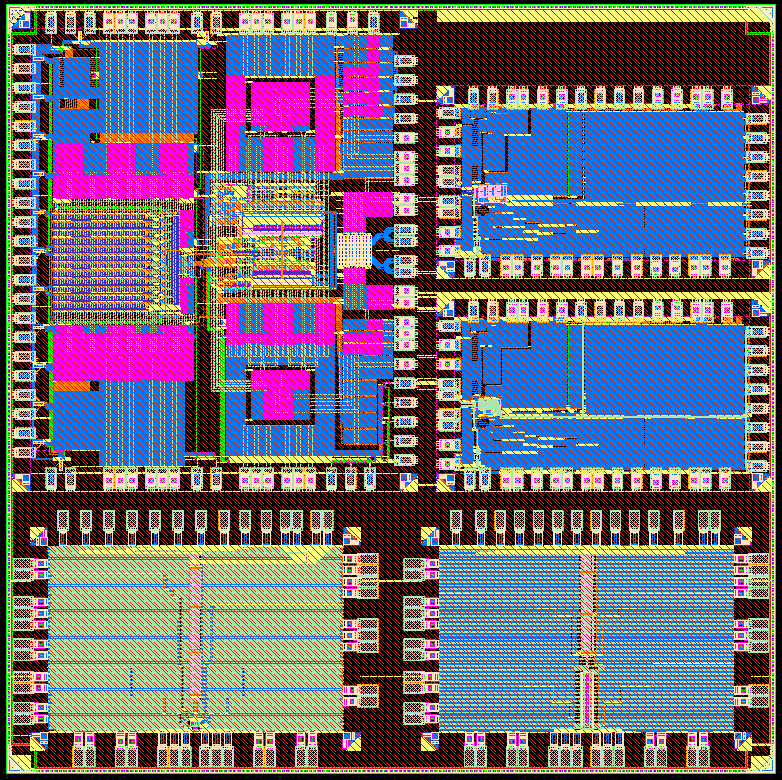

| IP개요 |

This thesis explores the design and implementation of Successive Approximation Register (SAR) Analog-to-Digital Converters (ADCs) with energy-efficient switching methods to meet the specifications of a 300MS/s 6-bit and a 50MS/s 10-bit ADC. The demand for high-speed ADCs for real-time data acquisition has spurred research into architectures capable of achieving fast conversion speeds. Flash ADCs offer high speeds but suffer from high power consumption and scalability issues. Pipelined ADCs provide a compromise between speed and power efficiency but are complex to design. SAR ADCs emerge as a solution due to their low power consumption, moderate speed, and high resolution. This study focuses on reducing SAR ADC power consumption through innovative switching methods: the Split Capacitor Method and Monotonic Capacitor Switching Method. The Split Capacitor Method splits the main MSB capacitor, reducing power consumption without additional clock phases. The Monotonic Capacitor Switching Method enables efficient switching in both directions, minimizing power consumption and improving reference settling. Experimental results demonstrate the efficacy of these methods in designing SAR ADCs meeting specific specifications. Circuit design methodologies, including CAD tools utilization, chip layout considerations, and simulation techniques, are detailed. Comparative analyses of the designed ADCs' performance metrics such as SNR, SNDR, DR, and power consumption are conducted |