| IP개요 |

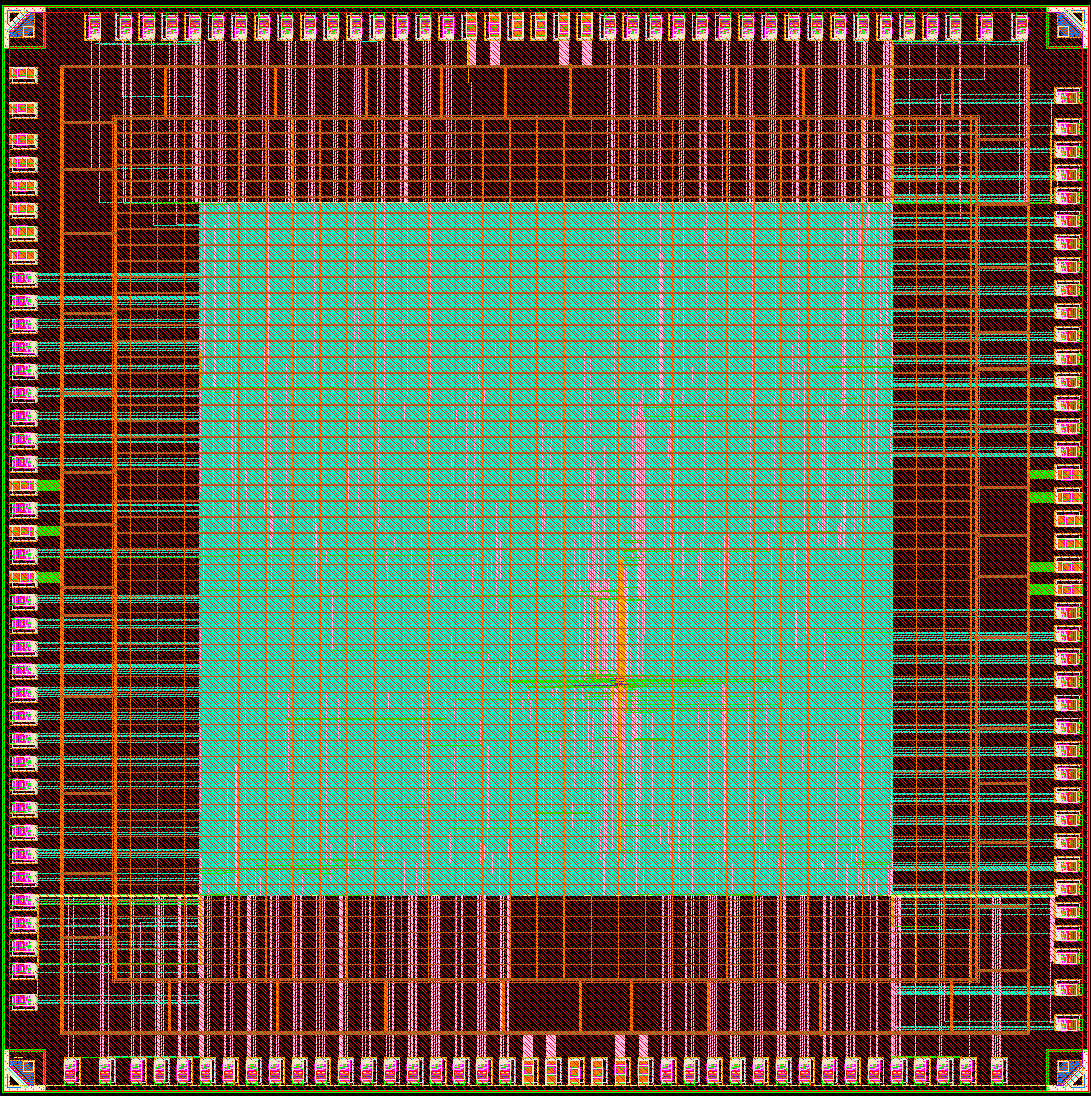

We propose an error correcting code encoder utilizing the orthogonal Latin Square code for HBM application. Recently, the AI industry's progress has led to the introduction of various AI(Artificial Intelligence) models, driven by the need for real-time access to computationally demanding applications like deep learning. This surge has intensified the demand for dedicated processors and high-capacity memory. To follow this trend, we designed the Error Correcting Code (ECC) system suitable HBM constructed by encoder and decoder. We designed the processor with Verilog HDL and verified the feasibility by simulation and implementing the design on a field programmable gate array (FPGA). We will fabricate the Error Correcting Code Encoder with Samsung 28nm FD-SOI (Fully Depleted-Silicon on Insulator) technology. The proposed system operates in 100MHz frequency, and the circuit is a digital type. |