| IP개요 |

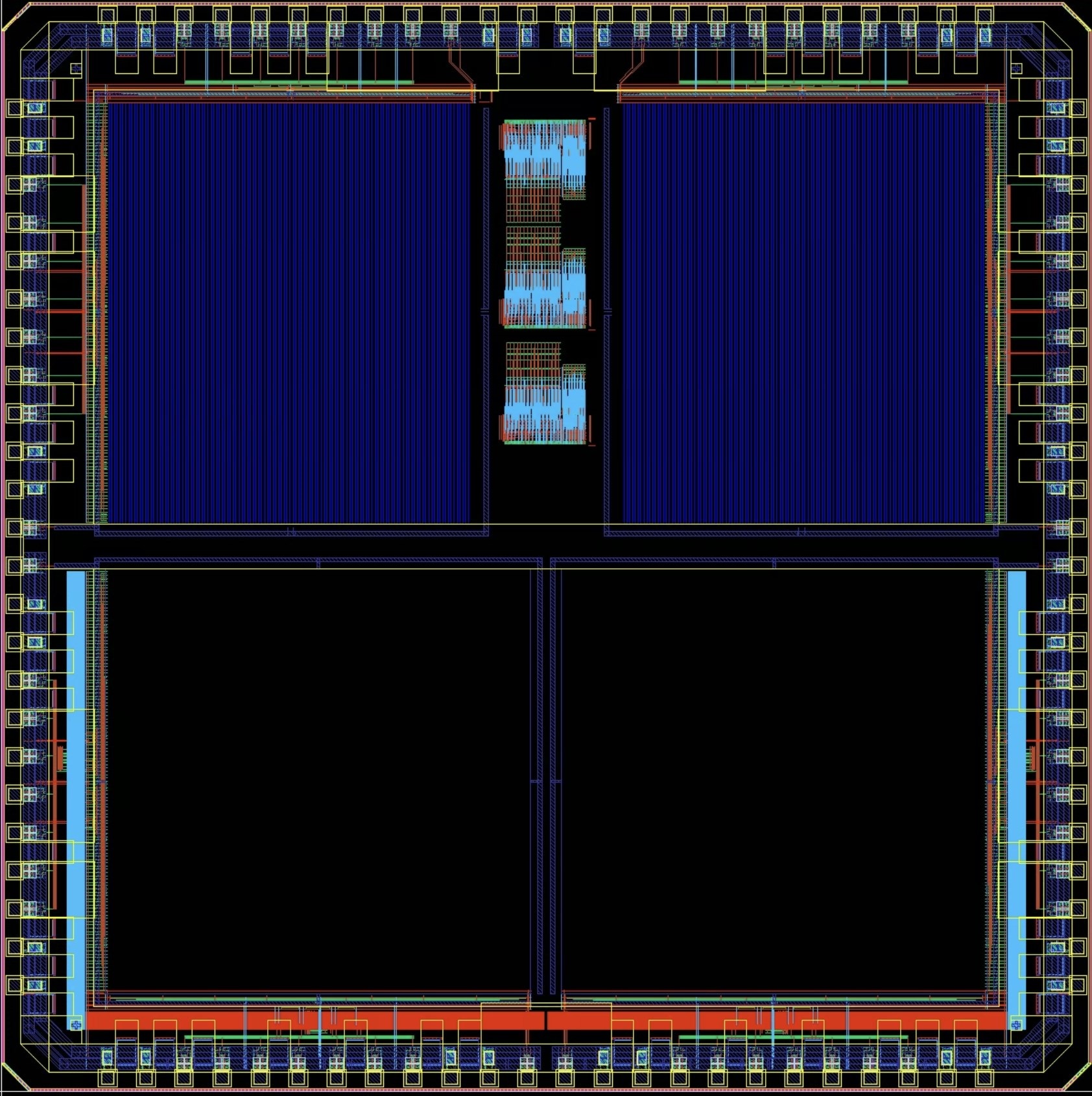

The design presents a low-power, low-distortion, miniaturized direct digital frequency synthesizer (DDS) for EIS sensing applications. It utilizes digital modulation to generate low-distortion sine waves by combining digitally synthesized sine wave data with an analog domain voltage output. This approach not only reduces the number of routing wires, pin assignments, and output registers after logic synthesis, but also enables the use of low-cost dynamic element matching (DEM) before interfacing with a digital-to-analog converter (DAC). The DDS with 10 bit amplitude resolution based on the nonlinear DAC with a maximum operating frequency of 10 MHz and capable of producing a minimum spurious-free dynamic range (SFDR) up to Nyquist frequency at the clock frequency. The prototype chip is fabricated in 180 nm CMOS technology and outputs a wideband sinusoidal frequency from 10 kHz to 10 MHz while consuming less than 1 mW of power. |