| IP개요 |

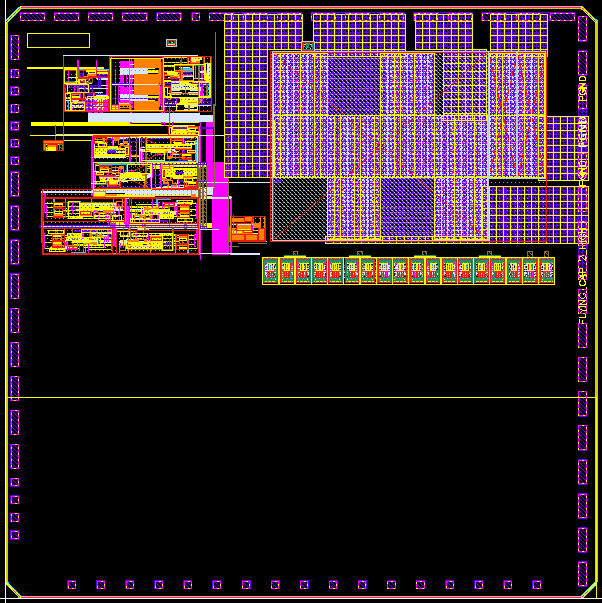

BCDMOS(Bipolar/CMOS/DMOS) 공정을 활용해, Printing Circuit Board(PCB)에 사용되는 External Capacitor를 줄일 수 있는 Open Loop based Calibration Three step down converter 구조에 대해 제안하고자 합니다. Power Management Integrated Circuit (PMIC)는 주로 Printed Circuit Board (PCB)에서, 외부 Inductor와 Capacitor를 사용해 Application(SoC/IoT/Display)에 정류된 전압을 제공합니다. 이러한 PCB에서 외부 Inductor, Capacitor의 면적이 큰 부피를 차지하게 되는데, 이 경우, PCB에 External Capacitor이 커지면서 전체 PCB의 면적 증가 및 Capacitor 개수 증가로 인해 전체 제품의 단가 상승으로 이어 지게 됩니다. 이러한 단점을 해결하기 위해, 기존 Conventional Buck Converter(CBC)의 2 Level topology(VIN →VOUT)와 달리 3 Level Topology(VIN → VIN/2→VOUT)을 통해 Output Voltage ripple을 줄여 External Capacitor와 Inductor를 줄일 수 있는 3 Level step down Converter 구조를 사용, 3 Level Converter의 가장 중요한 문제인 Flying Capacitor Voltage Balancing을 기존의 복잡한 구조의 Close loop based Calibration이 아닌, 전하공유(Charge Share)현상을 활용한 Open Loop based Calibration 구조의 Step Down Converter 입니다. |