| IP개요 |

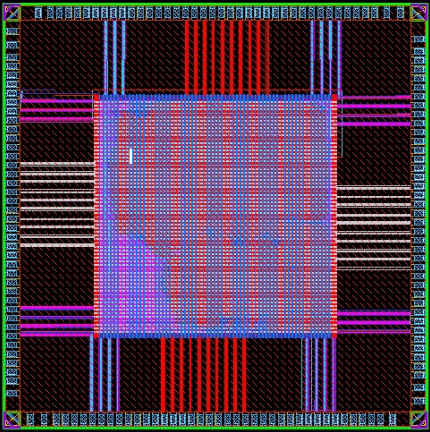

본 연구의 목표는 격자 기반 Post-Quantum Cryptography (PQC) 알고리즘을 가속하기 위한 하드웨어 설계로, 다가오는 Quantum Computing 시대를 대비한 Hardware Security System 구현에 있다. 특히, 격자 기반 PQC 알고리즘은 Ring Learning with Error (RLWE)를 활용하고 있으며, 이는 plain text를 N-1차의 polynomial로 변환하여 암호화 알고리즘에 필요한 연산들을 수행한다. 특히, RLWE를 활용한 알고리즘에서는 두 polynomial의 곱셈 연산 수행을 위한 Number Theoretic Transform (NTT)와 Inverse NTT (INTT) 연산을 굉장히 많이 필요로 한다. 따라서, NTT와 INTT 연산 속도 향상과 비용 효율성을 동시에 도모하기 위해 NTT와 INTT 연산이 동시에 가능한 bidirectional butterfly를 설계하였으며, NTT/INTT stage 별로 pipelining 구조를 제안하여 연산 속도 향상을 도모하였다. |