| IP명 | Two-step Classification Neuron Circuits for Low-power and High-integration SNN Systems | ||

|---|---|---|---|

| Category | Mixed | Application | AI |

| 실설계면적 | 4000㎛ X 4000㎛ | 공급 전압 | 1/1.8V |

| IP유형 | Hard IP | 동작속도 | 10MHz |

| 검증단계 | Simulation | 참여공정 | SS28-2401 |

| IP개요 | MNIST 추론 가능한 스파이킹 뉴럴 네트워크 시스템 구현 및 2단계 분류법을 활용하여 뉴런의 집적도 문제를 해결한다. 막전위를 쌓기 위한 멤브렝인 커패시터의 크기를 1/n배 줄이게 되면 서브포스트는 기존 메인 스파이크 개수를 n배로 증가시키고, 메인 포스트 스파이크와 서브포스트 스파이크 카운터를 활용해 2단계 분류하여 정확도를 향상시킨다. | ||

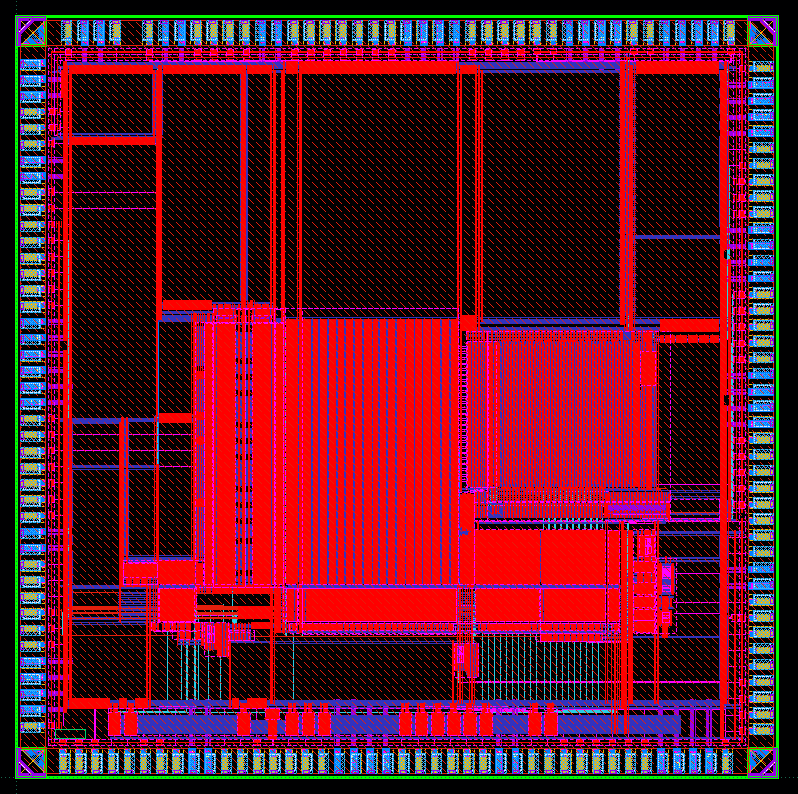

- 레이아웃 사진 -

|

|||