| IP명 | Integrated Bias-Controlled Avalanche Photodetector for 28 Gb/s Monolithic Optical Receiver in 28nm CMOS | ||

|---|---|---|---|

| Category | Analog | Application | IO Interconnect |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1.2V |

| IP유형 | Hard IP | 동작속도 | 28GHz |

| 검증단계 | Silicon | 참여공정 | SS28-2401 |

| IP개요 | Avalanche photodetectors (APDs)는 높은 multiplication gain으로 optoelectronic(O/E) receivers(RXs)의 성능을 크게 향상시킬 수 있다. 하지만 고성능 APD 구현을 위해서는 화합물 반도체 공정을 필요로 해서 비용적인 면에서 그 응용이 매우 제한적이다. 본 연구에서는 850 nm 대역에서 동작 가능한 Si APD를 28 nm CMOS 공정으로 제작하고, O/E Rx 구현에 필요한 transimpedance amplifier (TIA)를 집적한다. 동시에 CMOS 공정의 제한으로 인한 APD의 성능 저하를 회로적 기법으로 보상하며, 주변 환경에 민감한 최적 APD bias voltage를 자동적으로 탐색, 유지하는 bias controller를 부착하여 최적 성능의 단일 chip CMOS O/E Rx를 구현한다 | ||

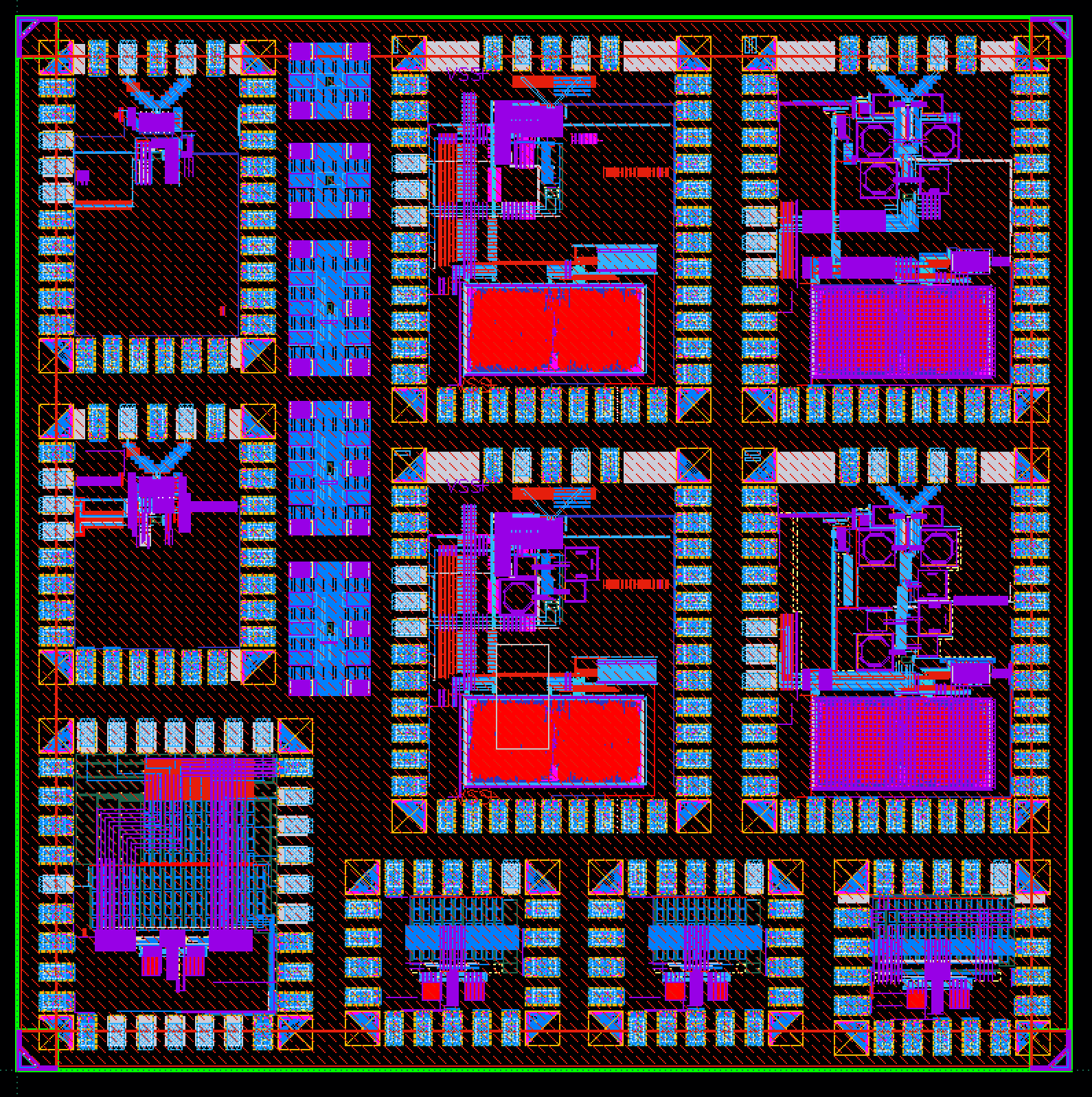

- 레이아웃 사진 -

|

|||