| IP명 | A 16Gbps DQ & 8GHz Clock Bi-Directional Pin Module System for Built-Out Self Test | ||

|---|---|---|---|

| Category | Mixed | Application | wireline interface |

| 실설계면적 | 2㎛ X 3㎛ | 공급 전압 | 1V |

| IP유형 | Hard IP | 동작속도 | 8GHz |

| 검증단계 | Silicon | 참여공정 | HM-2401 |

| IP개요 | 시스템 내 다중 채널의 skew를 인식 및 보상 하여 다중 채널의 동일한 신호를 주기 위해 설계된 회로다. cascaded PLL 과 Repeater 를 통해 clock jitter 와 SSN 을 최소화 하며, DLL과 PI 를 통해 채널 skew 조사에 필요한 high resolution clock 을 생성하였다. 이후 core 에서 training mode 를 통해 각 채널의 skew 정보를 조사 후 조사된 정보를 바탕으로 각 채널의 skew 를 동기화 하였다. 이를 통해 system은 고속에서 다중 채널로 채널간 전송 시간의 오류 없이 동작할 수 있는 self test 장비를 구축하게 된다. 이는 외부장비를 사용하지 않아 비용적인 측면에서도 큰 이득을 취하게 해준다. |

||

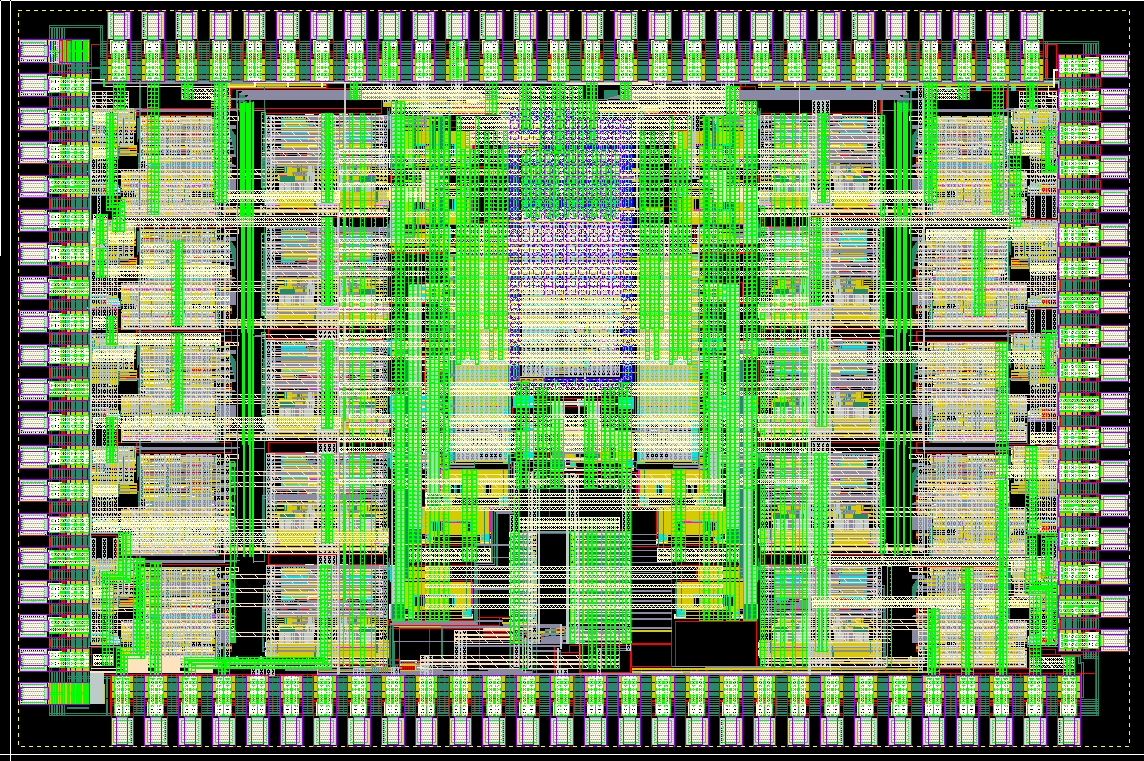

- 레이아웃 사진 -

|

|||