| IP명 | 144-to-162-GHz D-Band Frequency Synthesizer Using a Subsampling PLL and a Harmonic-Boosting Frequency Multiplier | ||

|---|---|---|---|

| Category | Analog | Application | Wireless Communication |

| 실설계면적 | 2.12㎛ X 3㎛ | 공급 전압 | 0.9/1.8V |

| IP유형 | Hard IP | 동작속도 | 144e9~162e9Hz |

| 검증단계 | Silicon | 참여공정 | HM-2401 |

| IP개요 | This work presents a D-band frequency synthesizer (FS) that can generate an ultra-low-jitter output signal over a large frequency-tuning range (FTR). To overcome the structural limitations of conventional sb-THz FSs and concurrently achieve a low jitter and a large FTR, this work was designed with a two-stage architecture in which a 50-GHz-band subsampling PLL with a 3rd -harmonic (HM)- rich class-F VCO at the first stage interoperated with an HMboosting frequency multiplier (FM) at the second stage. Designed with a 40-nm CMOS, this sub-THz FS exhibited a wide FTR of 11.8% (i.e., 144 to 162 GHz). Due to the highgain subsampling PD that can suppress in-band phase noise (PN) and the class-F VCO that can achieve low out-of-band PN, the proposed FS achieved the lowest RMS jitter (i.e., 45fsrms). Since the combination of the 3rd -HM-rich class-F VCO and the HM-boosting FM generated a D-band output signal in a power-efficient manner, this work also achieved the best jitter FOM among the state-of-the-art W/D-band FSs with an FTR more than 5%. |

||

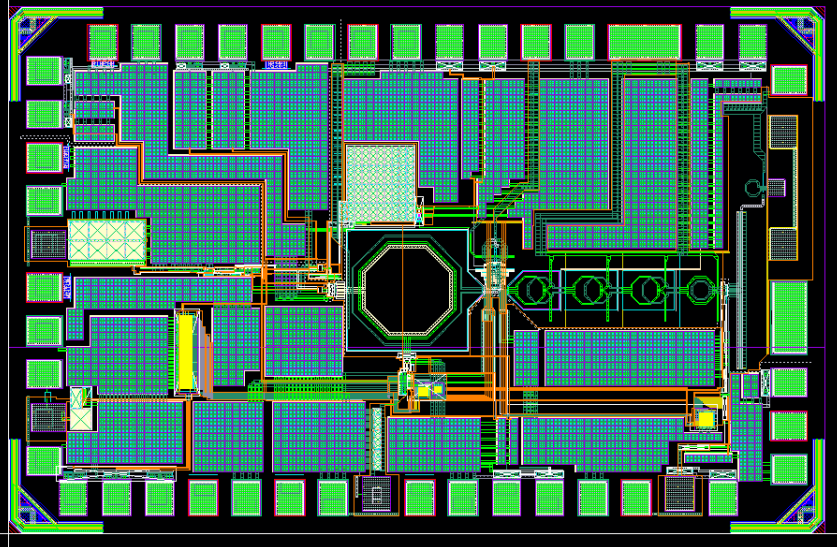

- 레이아웃 사진 -

|

|||