| IP명 | 0.6-7.7 GHz LO Generator Using a Single LC-VCO-Based Subsampling PLL and a Ring-Oscillator-Based Sub-Integer-N Frequency Multiplier | ||

|---|---|---|---|

| Category | Analog | Application | Wireless Communication |

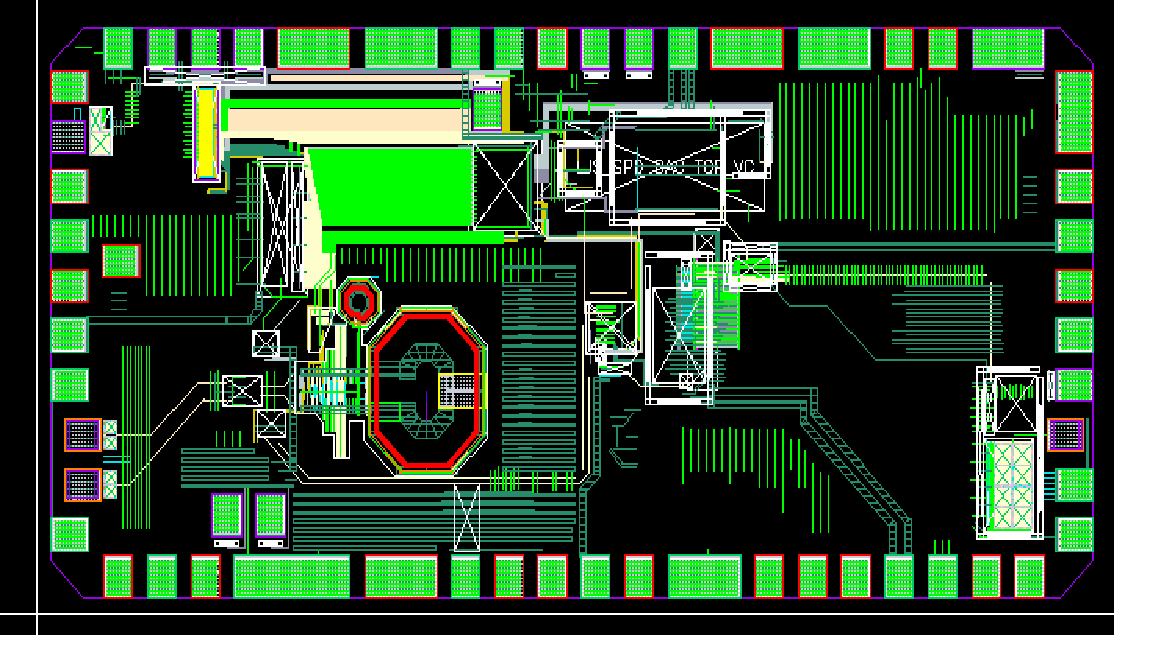

| 실설계면적 | 2.12㎛ X 3㎛ | 공급 전압 | 0.9/1.8V |

| IP유형 | Hard IP | 동작속도 | 0.6e9~7.7e9Hz |

| 검증단계 | Silicon | 참여공정 | HM-2401 |

| IP개요 | In this work, an ultra-low -jitter wideband cascaded local oscillation (LO) generator for 5G frequency range 1 (FR1) is presented. Using the phase-rotating divider (PRD) of the 2nd-stage ring-oscillator-based frequency multiplier (RO-FM) that can generate fractional multiplication factors (Ms), the required frequency-tuning range (FTR) of the 1st-stage phase-locked loop (PLL) dramatically decreased to 21%, which can be covered easily by a single low-phase-noise LC-voltage-controlled oscillator (VCO). Thus, the proposed LO generator can cover entire FR1 bands using only one LC tank. To suppress the fractional spurs caused by the mismatches of the delay cells of an RO, an individual-delay-cell-controllable digital loop filter (IDCDLF) was used to calibrate the mismatches. Since the IDCDLF equalizes the intervals between the quadrature signals of the RO, it can also naturally guarantee a precise quadrature relationship without any additional calibration. The 1st-stage PLL was designed based on a subsampling architecture, and it used a digital-to-analog converter (DAC)- based quantization error (Q-error) cancellation, dual-clockphase generator, and a third-order curve fitting digital predistortion (TCF-DPD) to achieve ultra-low phase noise |

||

- 레이아웃 사진 -

|

|||