| IP명 | Input-Jitter-Filtering DPLL Based Quadrature Clock-Generator for High-Speed DRAM Interface | ||

|---|---|---|---|

| Category | Analog | Application | DRAM Interface |

| 실설계면적 | 2.21㎛ X 3㎛ | 공급 전압 | 0.9/1.8V |

| IP유형 | 동작속도 | 1e9~4e9Hz | |

| 검증단계 | Silicon | 참여공정 | HM-2401 |

| IP개요 | This paper presents 1-4 GHz Input-Jitter-Filtering Digital-PLL Based Quadrature Clock Generator for Ultra-LowPower Clock Distribution in High-Speed DRAM Interfaces. By adopting DPLL in the clock distribution scheme, it filters out jitter. Additionally, it uses only one routing to generate accurate quadrature phases, which leads to dramatic reduction on power consumption. This scheme can be used in modern high speed DRAM interfaces, such as HBM, SDDR, GDDR. |

||

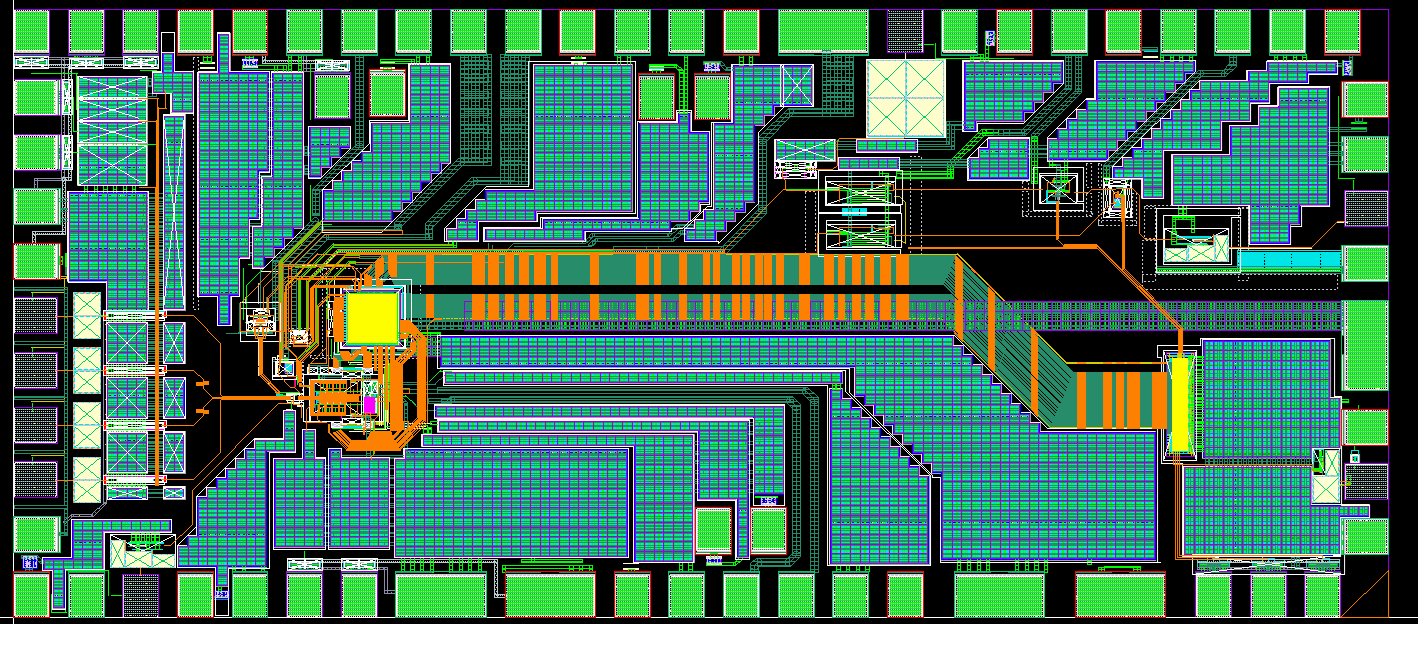

- 레이아웃 사진 -

|

|||