🌳본격적인 여름의 시작, 초록이 싱그러운 7월입니다.🌿

벌써 한 해의 절반이 지나갔네요. 남은 절반 연초에 하려고 마음먹었던 일들을 다시 한번 돌아보고 차분히 실천하면 좋을 것 같습니다.😝

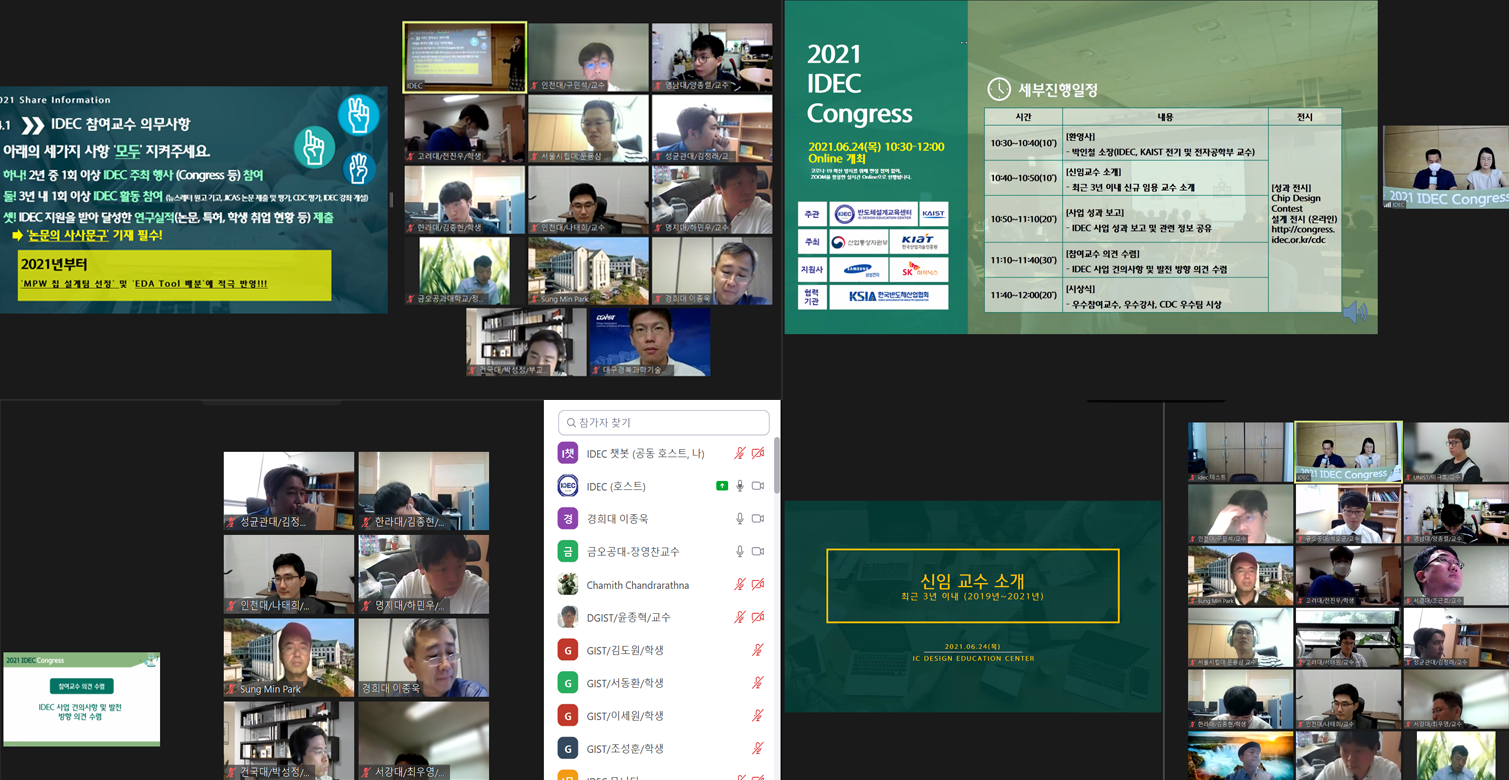

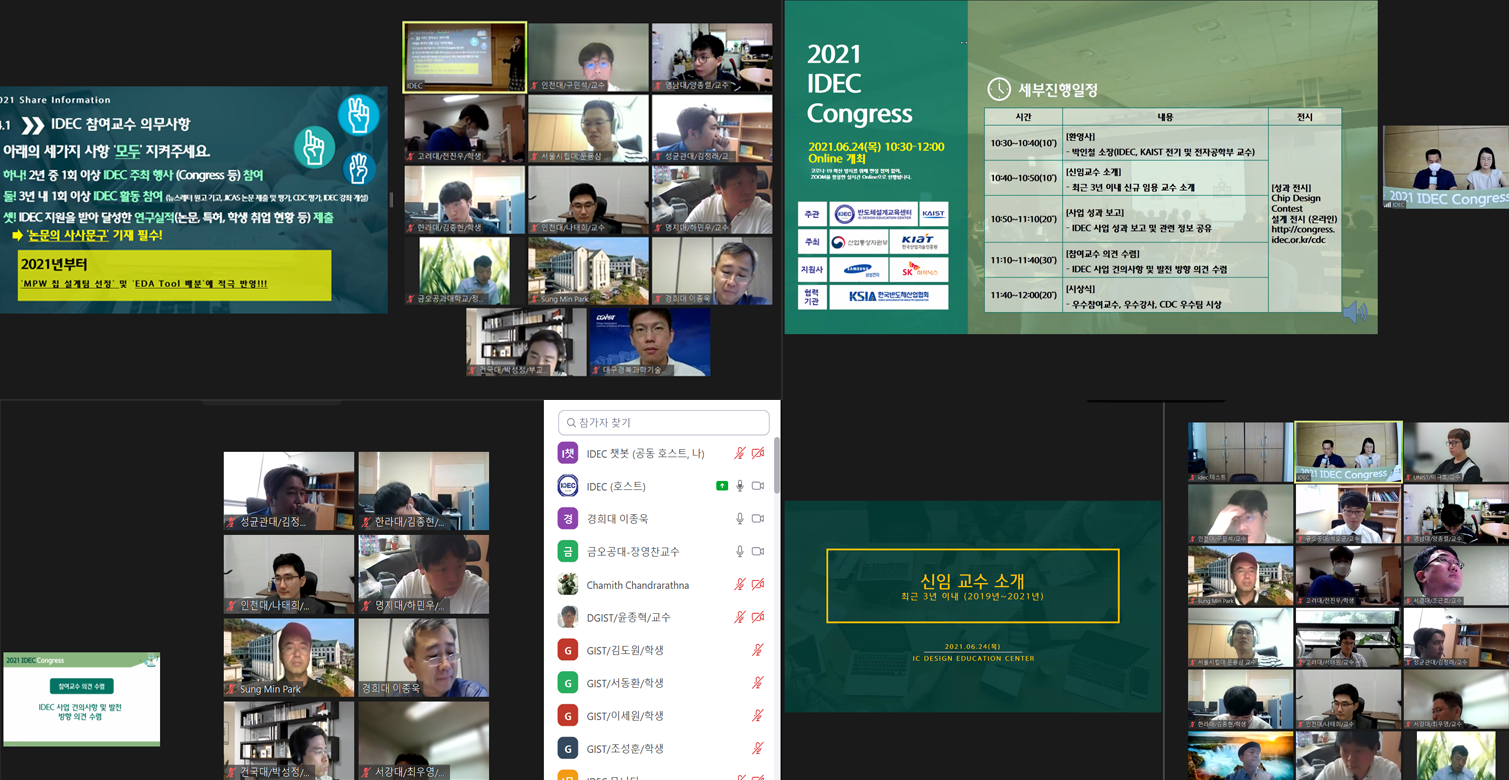

IDEC에서는 지난달 온라인으로 2021 Congress 개최했습니다. 코로나로 프로그램을 축소하여 진행했지만 많은분들의 관심과 참여 속에 잘 마무리 되었습니다.

코로나 백신 접종 속도가 빨라지면서 모든 일상이 제자리를 되찾을 것이라는 기대가 커지고 있습니다.

내년에는 IDEC Congress를 포함하여 IDEC 강의, 설명회 등 관련 일에 마스크를 벗고 직접 만날 수 있는 그날이 빨리 오기를 기대하며 모두 화이팅해요!🤭

|

IEEE Custom Intergrated Circuits Conference Review

|

2021년 교육 일정

7월-9월 강좌 목록을 확인하세요👀

하기 일정은 추후 변동될 수 있으며, 홈페이지를 통해 계속 업데이트될 예정입니다.

|

| 구분 |

강의일정 |

기간 |

강좌종류 |

강의제목 |

강사 |

소속 |

| 7월 |

7.5-9 |

5일 |

칩설계검증 |

Cell-Based Chip Design Flow 교육(1차) |

선혜승 연구원

김연태 연구원

노승수 소장 |

IDEC, Uxfactory |

| 7.13-15 |

3일 |

칩설계검증 |

Full-custom Chip Design Flow 교육 |

조인신 연구원 |

IDEC |

| 7.16 |

1일 |

설계강좌 |

PLL설계와 Jitter 해설 |

심재윤 교수 |

포항공대 |

| 7.21-23 |

3일 |

설계강좌 |

Xilinx FPGA HW 구성 이해 및 설계 |

김민석 팀장 |

리버트론 |

| 7.29-30 |

2일 |

Tool강좌 |

SiliconSmart / Liberary characterization |

신우철 차장 |

Synopsys |

| 8월 |

8.2-4 |

3일 |

설계강좌 |

(가제) VLSI 신호처리 |

이영주교수 |

포항공대 |

| 8.5-6 |

2일 |

설계강좌 |

뉴럴인터페이스 회로 설계 |

김철교수 |

KAIST |

| 8.9-10 |

2일 |

Tool강좌 |

반도체 공정/소자 시뮬레이션을 위한 Synopsys TCAD - Sentaurus Basic Training (2차) |

김나라 과장 |

Synopsys |

| 8.11-12 |

2일 |

Tool강좌 |

Low Power Flow(BE) |

박병하 과장 |

Synopsys |

| 8.17-19 |

3일 |

Tool강좌 |

CustomCompiler Schematic/Layout Editor (1차) |

김민수 과장 |

Synopsys |

| 8.24-25 |

2일 |

설계강좌 |

가제: XMODEL |

김재하 교수 |

서울대 |

| 8.26-27 |

2일 |

Tool강좌 |

Finesim |

김장원 부장 |

Synopsys |

| 9월 |

9.1 |

1일 |

설계강좌 |

MATLAB 알고리즘의 C코드 생성 워크플로우 |

정승혁 차장 |

매스웍스코리아 |

| 9.2-3 |

2일 |

설계강좌 |

MATLAB으로 시작하는 Machine Learning 및 Deep Learning |

김종남 부장 |

매스웍스코리아 |

| 9.6-8 |

3일 |

설계강좌 |

Xilinx ZYNQ 기반의 SoC 설계 (2차) |

김민석 팀장 |

리버트론 |

| 9.9-10 |

2일 |

설계강좌 |

메모리 기반 하드웨어 인공지능 |

조성재 교수 |

가천대 |

| 9.13 |

1일 |

설계강좌 |

생체신호 수집을 위한 증폭기 및 신경 자극기 설계 기초 |

김정석 교수 |

가천대 |

| 9.14-16 |

3일 |

Tool강좌 |

PrimeTime 사용법 및 활용예 |

김태삼 차장 |

Synopsys |

| 9.28-30 |

3일 |

Tool강좌 |

IC Compiler 사용법 및 활용예 |

임동규 과장 |

Synopsys |

|

더보기..

|

교육 담당자 : 김영지 전임 (yjkim@idec.or.kr, 042-350-8536)

|

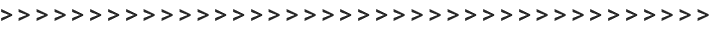

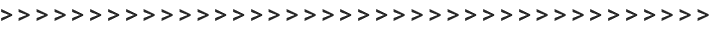

기초 교육 확대😆

학생들의 기초 향상을 위해서 IDEC에서는 칩 설계 기초 교육 컨텐츠를 개발 중에 있습니다.

현재 디지털 칩 설계 flow 강좌및 리눅스 기초 강좌가 유튜브에 업로드 되어 있습니다.

모든 영상은 30분 내외로 제작 운영 중이라고 하니 많은 관심 부탁드립니다.

혹시 아직 IDEC 유튜브에 구독을 하지 않으신 분들은 구독!! 좋아요!! 아시죠?

|

MPW 모집 일정 안내

🙋♀️2021년 MPW 지원 공정 및 내역🙋♀️

MPW는 대학에 연구와 교육을 위해 칩제작을 지원하는 프로그램이며, 지원대상은 IDEC 참여교수 입니다.

| 구분 |

공정사 |

공정내역 |

Package |

모집횟수 |

제작팀 |

| 지정공정 |

삼성전자 |

28nm RFCMOS 1-poly 8-metal |

208pin LQFP Type |

2 |

80 |

| DB Hitek |

180nm BCDMOS |

- |

1 |

15 |

| 희망공정 |

국내외 공정(TSMC 등) |

65nm-250nm BCD / RF / CMOS 등 |

- |

2 |

50 |

|

잠깐! 삼성 28nm 공정은 IDEC 클라우드 서버를 접속하여 설계를 진행합니다.

🙋♂️2021년 MPW 지원 일정 안내🙋♂️

(기준 : 06.08)

회차구분

(공정-년도순서) |

참여팀수 |

DB마감

(Tape-out) |

Die-out |

공정 |

| SS28-2101 |

40 |

2021.07.19 |

2021.12.31 |

삼성 28nm |

| SS28-2102 |

선정 중 |

2022.01.17 |

2022.06.30 |

| DB180-2101 |

23 |

2021.07.12 |

2021.11.05 |

DB Hitek180nm |

| HM-2101 |

21 |

Tape out(2021.04.20⁓09.10) |

2021.07⁓12 |

TSMC 공정 등

희망하는 국내외 공정 |

| HM-2102 |

선정 중 |

Tape out(2021.09⁓2022.01) |

2021.12⁓2022.04 |

MPW 담당자 : 이의숙 책임 (yslee@idec.or.kr, 042-350-4428)

|

|

Tool 변경 사항 안내

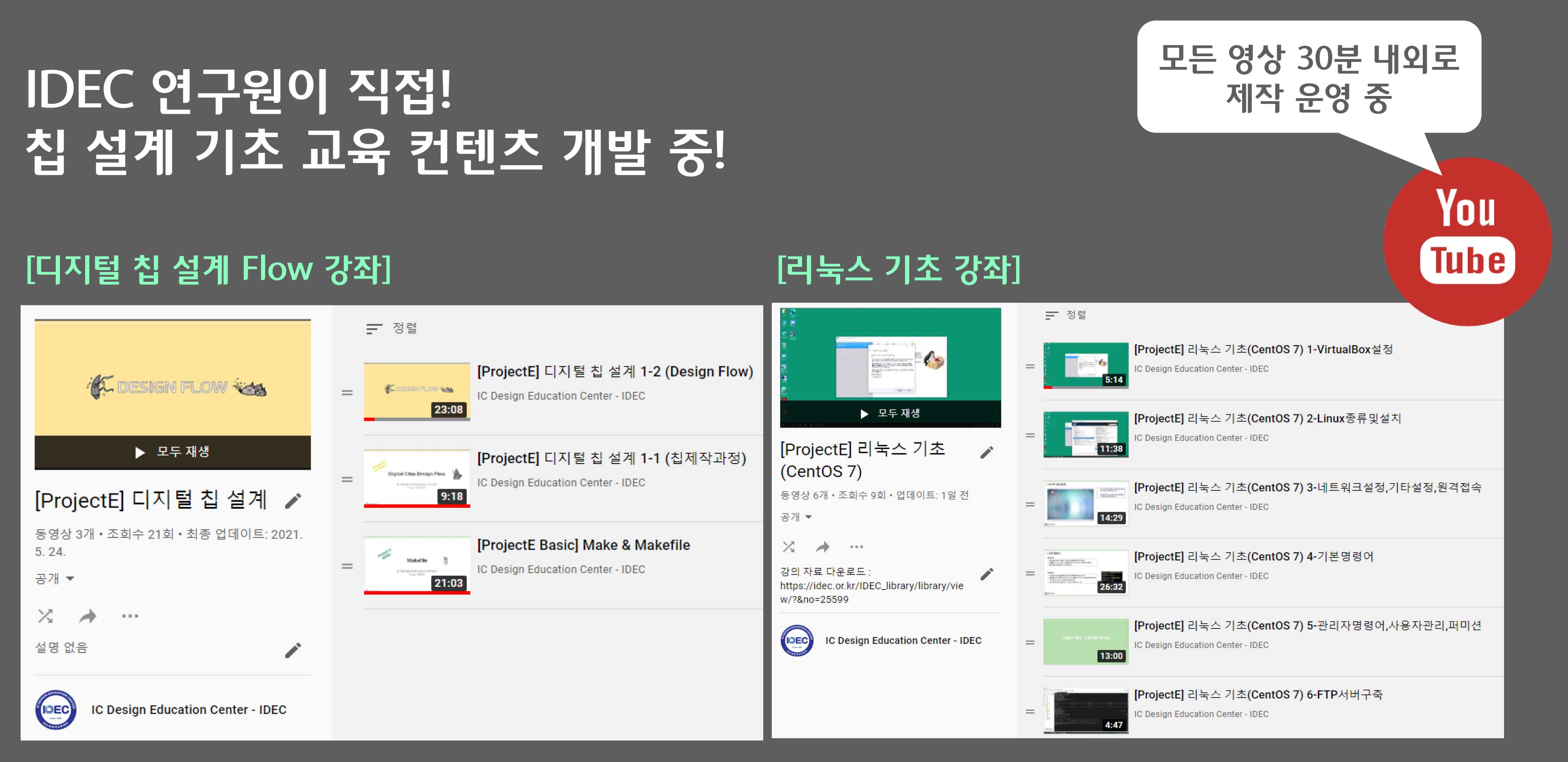

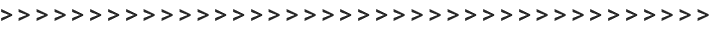

하나. 학부 교육용 Tool 지원 중단 안내🚫

2019년 2학기부터 학부생 대상으로 개설되는 대학 정규 강의에 활용하실 수 있도록 주요 Tool인 CADENCE, Siemens, SYNOPSYS을 제공했습니다. 하지만 올해는 전년도 대비 사업비 규모 축소로 인하여 학부 교육용 Tool 제공이 2021년 1학기를 마지막으로 중단됩니다. 추후 사업비 증액시 내부적으로 고민할 예정이며, 다시 학부용 Tool을 제공할 수 있도록 노력하겠습니다. 많은 관심 부탁드립니다.🙇♀️🙇♂️

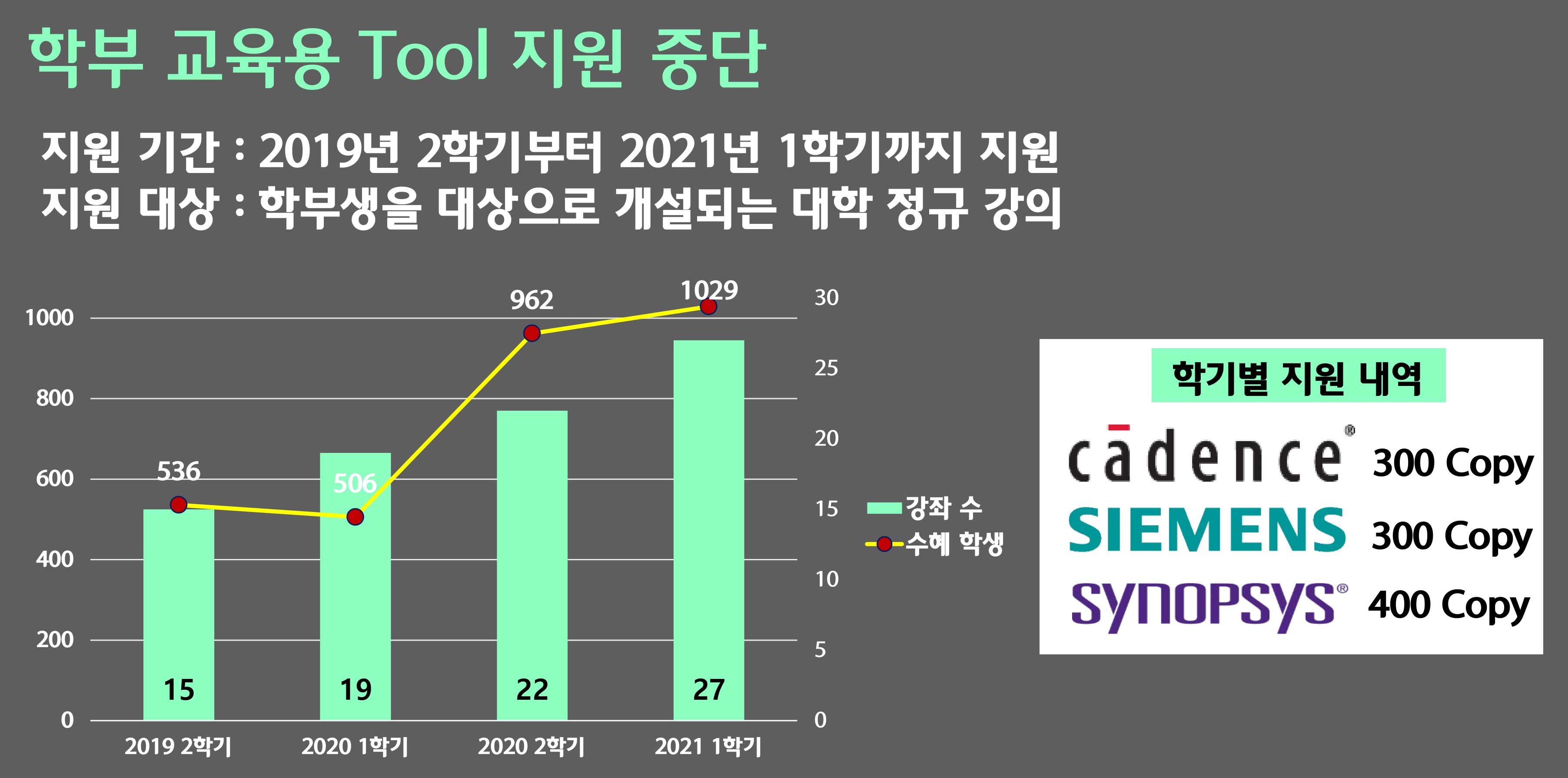

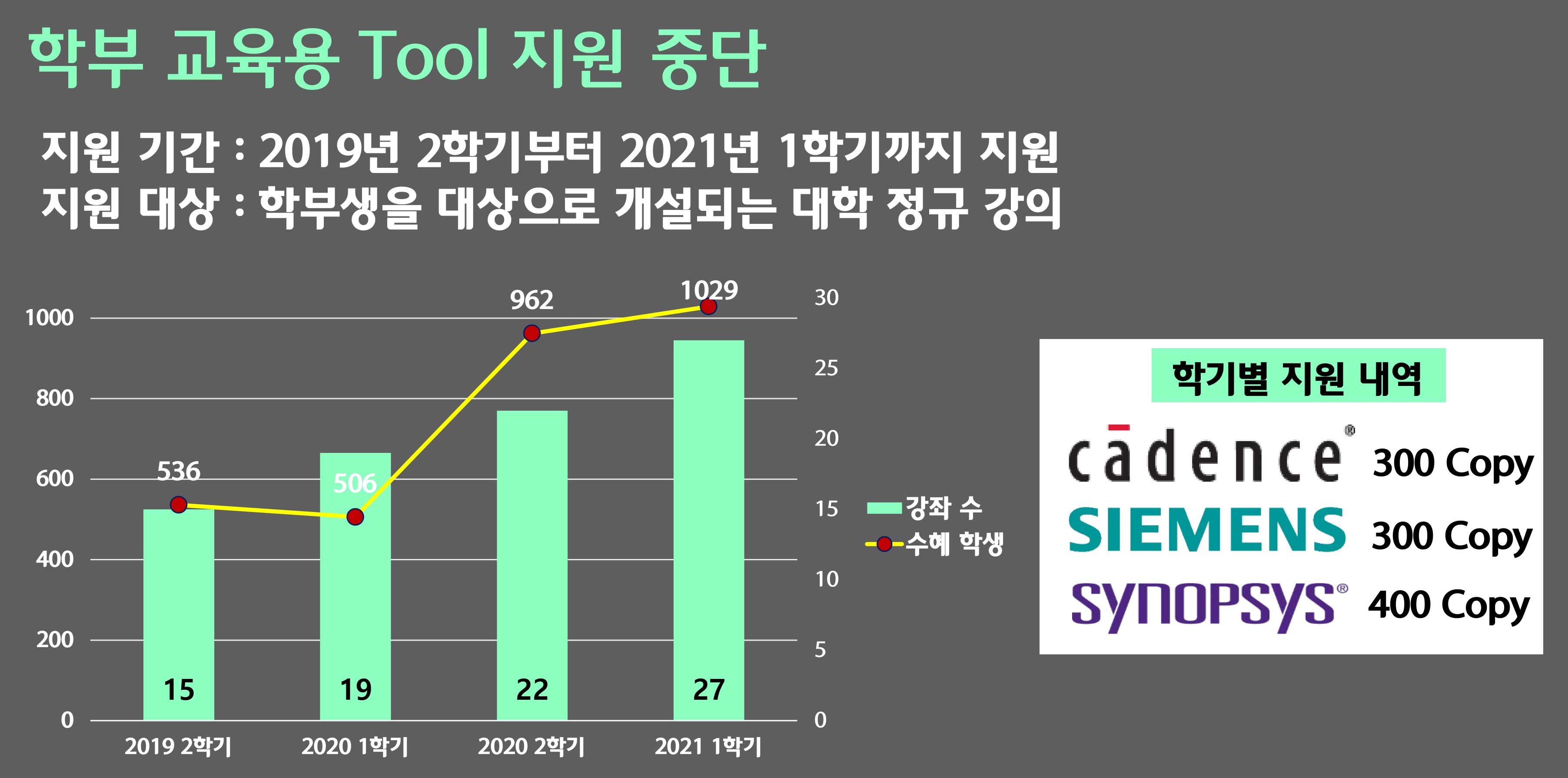

둘. Cadence Tool 소식!

🎉좋은 소식입니다.🎉Cadence Tool에서 Virtuoso Layout Suite Tool과 Schematic Editor Tool의 버전 업 소식입니다. 작년까지 L버전으로 제공되었던 해당 Tool이 XL 버전으로 제공됩니다. (상세내역 하단 참고)

그리고 MMSIM 사용시 시뮬레이션 시간을 최대 10배 단축할 수 있는 Spectre X를 사용할 수 있는 MMSIM with Spectre X가 제공될 예정이니 7월부터 사용시 참고해주시길 바랍니다.

① Layout Suite XL 세부 기능 다운로드

② Schematic editor XLSC 세부 기능 다운로드 (Constraint- and connectivity-driven layout 지원)

③ Spectre X 세부 기능 다운로드 (최대 10 배의 시뮬레이션 속도 향상 및 5 배의 용량 개선이 가능)

셋. 2021 신규 Tool 소개

- 배 경 : Arm사 SoC Designer의 서비스 종료(EOL)에 따른 버전 업데이트 중단 및 기술지원 불가로 인하여

신규 tool을 도입하여 지원을 지속하고자 함.

- Vendor사 및 Tool 명 : COSEDA 사 COSIDE

- 기능 : Virtual Platform (칩 제작 기간 동안 소프트웨어 개발 가능)

- 사용 기간 : 2021.07.01(목) 이후 네트워크라이선스 신청을 통해 상시 신청 가능

|

IDEC Congress 개최

2021년 6월 24일(목)에 온라인으로 진행되었어요. CDC 설계 전시 및 IDEC 사업 성과 보고와 관련 정보를 교류하는 자리였으며 많은 분들의 관심과 참여 속에 성황리에 마무리되었습니다. 아래 사진은 행사에 IDEC 참여교수와 참여학생들이 실제로 Zoom을 이용해서 온라인으로 참여한 모습입니다.

(IDEC Congress 홈페이지 바로가기)

2021년 IDEC Congress Chip Design Contest

2021년 6월 24일(목)에 개최된 IDEC Congress CDC입니다. 총 88팀이 참여했고, 2021 IDEC CDC Best Design Award은 3팀, 2021 IDEC Congress CDC Best Poster Award 5팀을 선정하였습니다.👏아래는 수상내역입니다. 모두모두 축하드려요.👏

| 시상명 |

소속 |

지도교수 |

주저자 |

논문명 |

상금 |

| 2021 IDEC CDC Best Design Award |

경희대 |

이종욱 |

Seneke Chamith Chandrarathna |

A 416 nW Buck-Converter with Dynamically-Configured and Adaptively-Controlled Direct MPPT for Triboelectric Energy Harvesting with 88% Peak Efficiency |

100만원 |

| KAIST |

최재혁 |

박선의 |

An 82fsRMS-Jitter 102GHz W-Band PLL Using a Power-Gating Injection-Locked Frequency Multiplier-Based Phase Detector |

| 고려대 |

김철우 |

박인호 |

A Bidirectional High-Voltage Dual-Input Buck Converter for Triboelectric Energy-Harvesting Applications |

| 2021 IDEC Congress CDC Best Poster Award |

KAIST |

최재혁 |

박선의 |

An 82fsRMS-Jitter 102GHz W-Band PLL Using a Power-Gating Injection-Locked Frequency Multiplier-Based Phase Detector |

20만원 |

| KAIST |

배현민 |

권순원 |

A Fully Digital Semirotational Frequency Detection Algorithm for Bang–Bang CDRs |

| 중앙대 |

백광현 |

한재섭 |

Conversion Speed Regulation SAR ADC with compensation for PVT variations |

| 경희대 |

이종욱 |

Seneke Chamith Chandrarathna |

A 416 nW Buck-Converter with Dynamically-Configured and Adaptively-Controlled Direct MPPT for Triboelectric Energy Harvesting with 88% Peak Efficiency |

| 충남대 |

고형호 |

최규리 |

Open-loop Nanoresonator Integrated Circuit for Motional Resistance Sensing |

2021 ISOCC Chip Design Contest

ISOCC는 2021년 10월 6일부터 9일까지 제주 라마다호텔에서 개최예정이며 CDC 진행 일정은 아래를 참고하세요.

| 참여신청일 |

평가일정 |

발표자료 제출기간 |

CDC 개최 |

| ⁓2021.07.09 |

2021.07.16⁓07.30 |

2021.08.16⁓08.30 |

2021.10.07 |

|

📣홍보📣

"반도체 분야 기업을 소개합니다.

안녕하세요. 주식회사 알파솔루션즈입니다.

주식회사 알파솔루션즈는 고해상도 디스플레이 데이터를 송/수신하는 HDMI, LVDS, MIPI C-PHY/ D-PHY IP를 국내/외 주요 기업에 판매 및 양산하고, DisplayPort, MIPI A-PHY 등의 기술을 연구 개발하는 인터페이스 전문 반도체 팹리스 기업입니다.

지난 2010년 High Speed Interface IP 분야에서 세계를 선도하는 기술 및 제품 개발을 목표로 설립되었으며, 2012년 HDMI1.4 Rx/Tx IP 개발 및 License 출시와 양산을 시작으로, 현재의 HDMI 2.1 Rx/Tx IP, MIPI C-PHY/D-PHY 이르기까지 끊임 없는 기술 개발과 연구를 거듭해오고 있습니다.

알파솔루션즈는 최고의 경쟁력을 가진 최신의 IP 기술을 개발하기 위해, 관련 표준 개발에 적극적으로 참여하고 독창적인 구조를 도출하여 최신의 공정에 최적화된 최신 인터페이스 기술을 앞서 개발하는 전략을 추구해오고 있습니다.

2017년부터는 삼성전자 파운드리 사업부의 FinFET 공정용 최첨단 IP 개발 및 License를 공급하는 SAFE Design Partner로서, 현재는 전세계 Tier-1까지의 SoC 기업에 4nm부터 14nm까지의 FinFET IP를 License 하고 있으며, 글로벌 시장에서 세계 1류 기술을 보유한 기업으로 인정 받고 있습니다.

알파솔루션즈는 업계 최고의 Power, Performance, Area(PPA)를 구현하기 위한 구조, 회로설계, 양산 대응 기술등을 연구 개발하여 왔으며, 이러한 개발 기술을 적용한 IP를 통해 제품 경쟁력을 구현하고 있습니다.

또한, 알파솔루션즈의 IP는 MPW를 통하여 포괄적인 테스트를 거친 실리콘 검증된 IP로 제공됩니다. 양산을 위해 고유의 BIST 기능을 내재한 IP는 신호 품질 지원을 위한 S/I, P/I 지원, 소프트웨어 지원을 위한 F/W, 응용 회로 지원을 위한 H/W 지원을 포함한, 빠른 고객 대응력을 통해 고객사 Trouble Shooting 및 양산을 지원하는 강점을 가지고 있습니다.

주식회사 알파 솔루션즈는 앞으로도 고객사와의 유기적인 협력 관계를 유지하며 지속적인 지원과 신뢰를 확보하는 것은 물론, 끊임없는 연구 개발을 통해 글로벌 시장에 최고의 IP를 개발 공급하도록 최선을 다하겠습니다.

현재 저희 회사의 필요한 인재를 수시로 채용 중이니 언제든지 메일을 보내주시기 바랍니다.

|

|

(34141) 대전 유성구 대학로291 한국과학기술원 N26동 CHIPS건물 IDEC

(Tel : 042-350-8532)

|

|