# IDEC Chip Design Contest

3T1C\_P

Pull up

eDRAM based digital computing in memory neural network accelerator with enhanced retention time

<sup>1</sup>Inhwan Lee, <sup>1</sup>Hyunmyung Oh, <sup>2</sup>Jehun Lee, <sup>2</sup>Jaeyong Jang and <sup>2</sup>Jae-Joon Kim

<sup>1</sup> Pohang university of science and technology (POSTECH) <sup>2</sup> Seoul National University

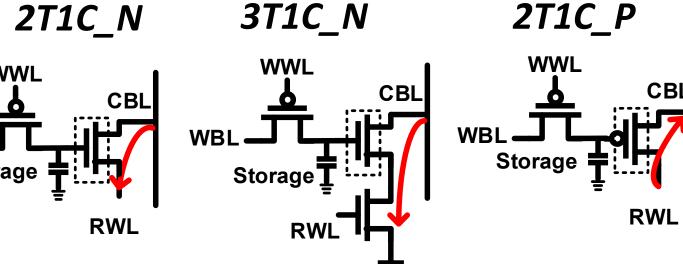

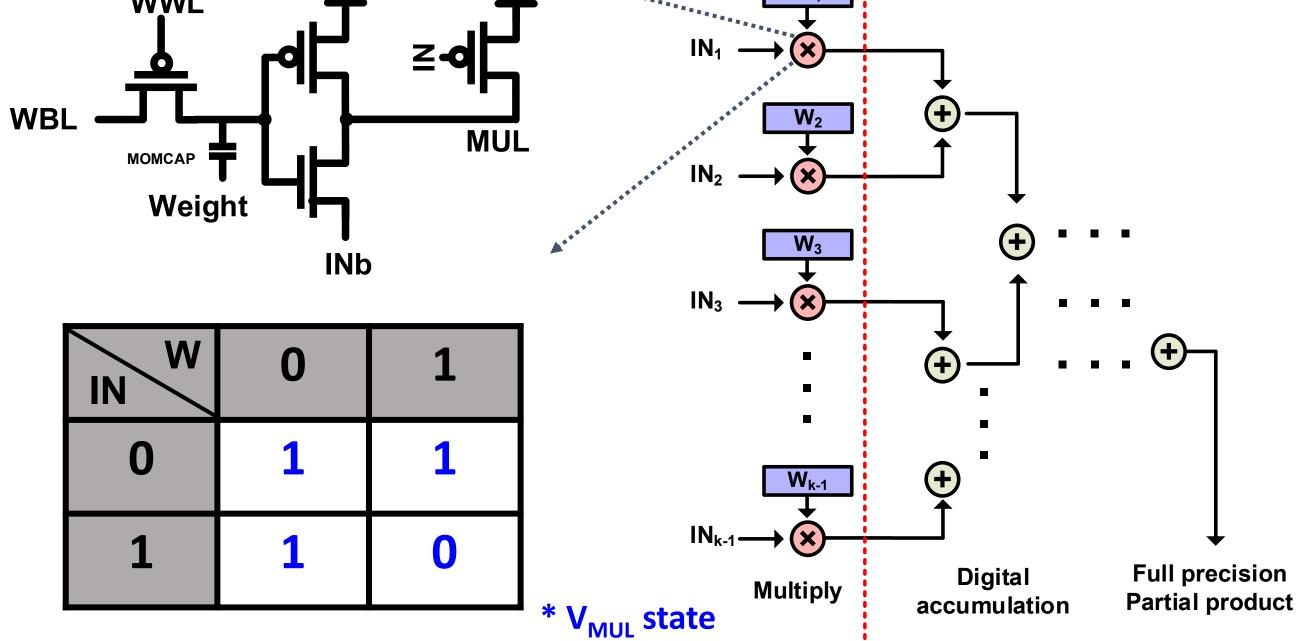

#### Background Motivations of eDRAM based NN accelerator Previous research SRAM cell based CIM design eDRAM cell based CIM design **Capacitive Cell Resistive Cell** 2T1C\_N 2T1C\_P 3T1C\_N

WL BL

Non-linear operation, instability due to PVT variation SRAM cells have large cell sizes that limit their memory capacity

BLb Linear operation, stability from

**PVT** variation

There is a need for smaller cell sizes to overcome the issue of limited memory capacity.

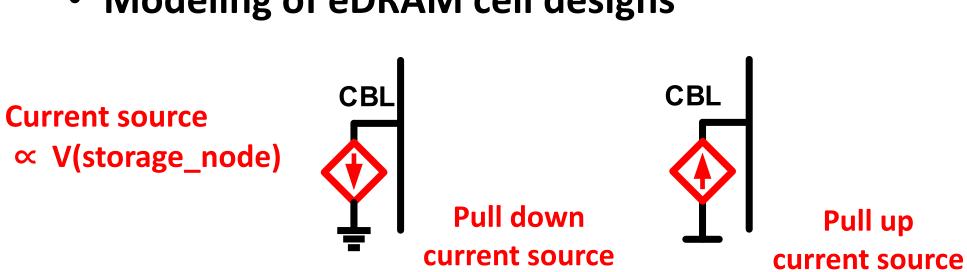

Modeling of eDRAM cell designs

Advantage **Utilize 2 to 4 transistors** to implement CIM operation with a smaller cell size.

Logic compatible with **CMOS** process

- Disadvantage **✓** Currents are vulnerable to PVT variation ✓ Unstable output value

- due to leakage current **✓** Short retention time

## Proposed eDRAM array

Increased retention time

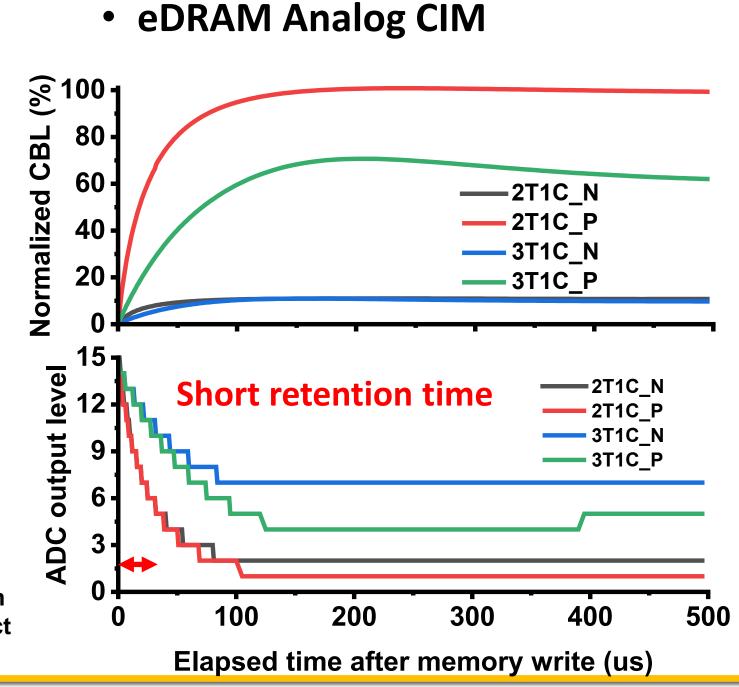

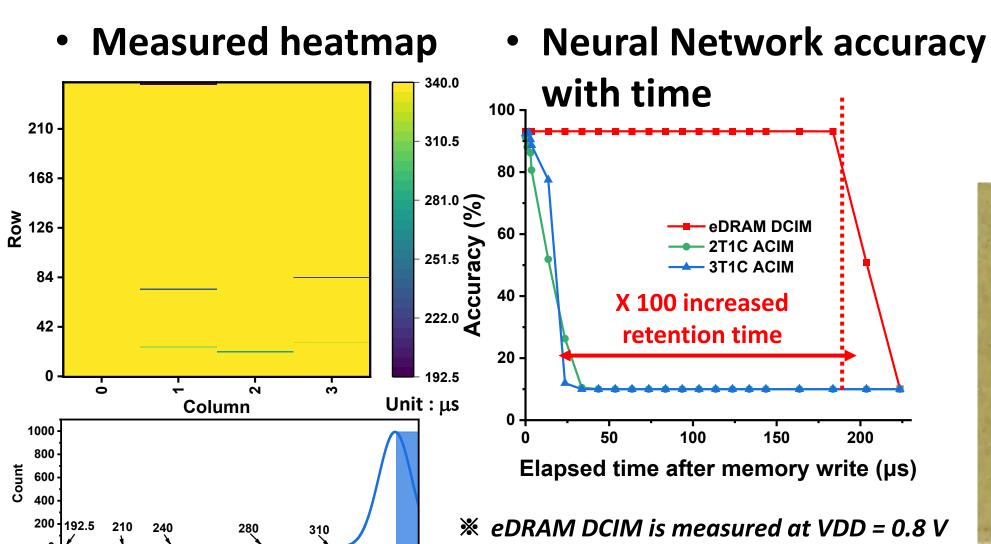

eDRAM Digital CIM **0.8** · **S**<sub>0.6</sub>-€<sub>0.8</sub>. **Long retention time** 100 150 200 250 300 350 400 Elapsed time after memory write (us)

### Evaluation

#### CIM operation 其 3000 2500 **2000** = 1500 -All MAC value can be expressed <mark>용</mark> 1000 by adder tree without accuracy loss 1000 1500 2000 2500 3000 3500 **MAC** value MAC value is kept long due to DCIM operation Elapsed time after memory write (us)

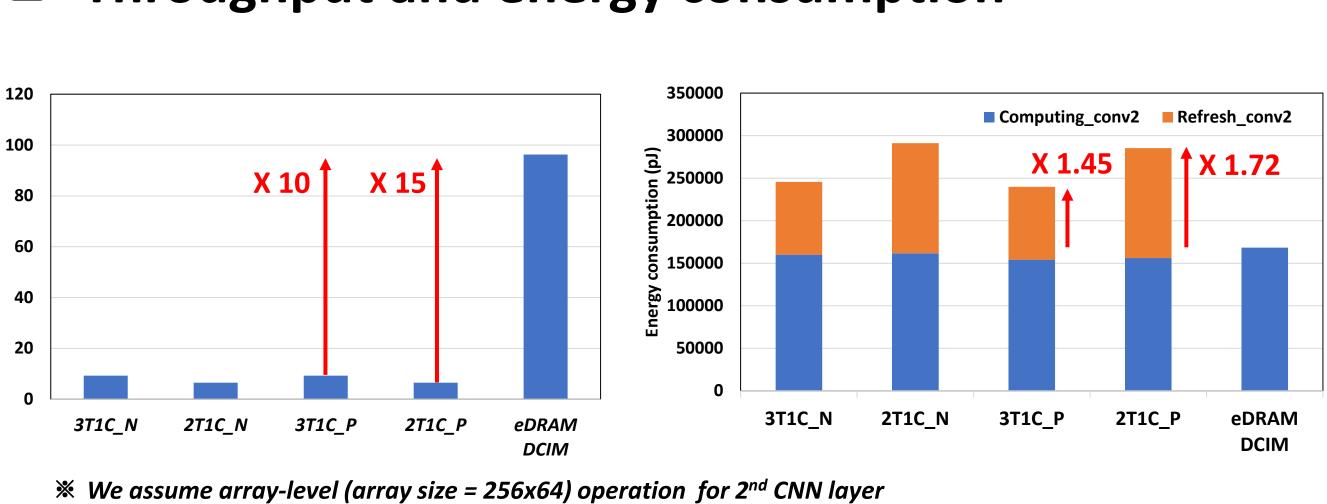

Throughput and energy consumption

$\divideontimes$  ACIM supply voltage = 1.0 V, DCIM supply voltage = 1.0 V for Core cell and 0.7 V for Peripheral circuit.

Retention time

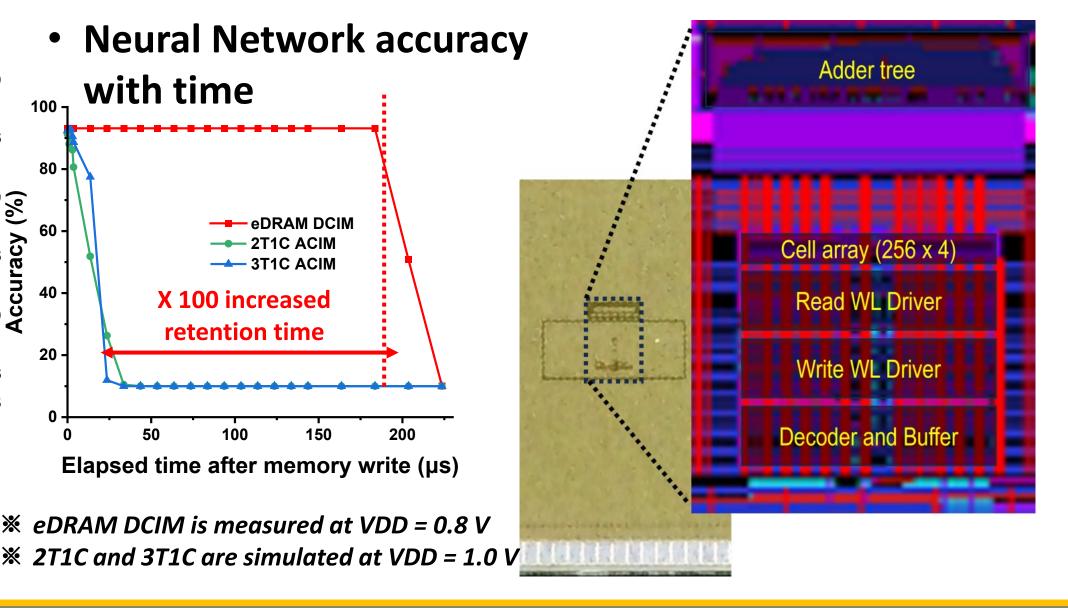

Die photo and layout of eDRAM array

| Technology                 | 28 nm CMOS              |

|----------------------------|-------------------------|

| Supply voltage (V)         | 1.0                     |

| Frequency (MHz)            | 70                      |

| Input / Weight /<br>Output | 4/4/<br>12              |

| Array size                 | 256x4<br>(1kb)          |

| Total Area                 | 190.7 um x<br>227.25 um |

# Conclusion

- A novel eDRAM cell mimicking a digital logic gate for digital CIM operation is proposed

- Long retention time and accurate MAC values are accomplished due to DCIM operation

- x 15 increased throughput and x 1.7 reduced energy consumption is obtained due to enhanced retention time.

## Acknowledgement

The EDA tool was supported by the IC Design Education Center (IDEC), South Korea.